נציגי AWS ואנסיס טוענים כי השיטה ההיררכית שפיתחו מאפשרת לקבל זמן תגובה מהיר יותר, כיסוי רחב יותר ותשתית מחשוב זולה יותר – שלושה פרמטרים קריטיים בעידן שבו מאיצי AI בעלי מיליארדי טרנזיסטורים ואריזות 2.5D/3D הופכים לסטנדרט.

בכנס 2025 TSMC Europe Open Innovation Platform Ecosystem Forum, שהתקיים בשבוע שעבר באמסטרדם, הציגו מהנדסי AWS Annapurna Labs וחברת אנסיס (Ansys) שיטה חדשה לקיצור דרמטי של זמני ניתוח ה-IR-drop במערכות-על שבב מורכבות – במיוחד במאיצי AI מבוססי אריזה דו-ממדית וחצי (2.5DIC) עם זיכרון HBM.

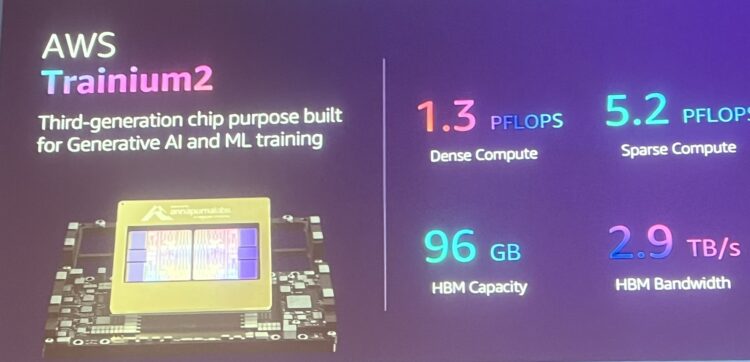

הלמוט בלדליך, מומחה מחברת אנסיס (Ansys), הציג בכנס SMC 2025 Europe Open Innovation Platform Ecosystem Forum שהתקיים בשבוע שעבר באמסטרדם כיצד ניתן לקצר בצורה דרמטית את זמני ניתוח ה-IR-drop וה-EMIR בצ’יפ Trainium של AWS, באמצעות מודלים מצומצמים (ROM) וזרימת עבודה היררכית.

המאיץ שעל פריסתו דוּוח בכנס הוא שבב ייעודי לאימון מודלי GenAI, המיוצר בתהליך מתקדם ויושב על גבי אינטרפוזר אורגני עם חבילת HBM בהיקף עשרות גיגה־בייט. מדובר ב-SoC ענק, הכולל מיליארדי תאי לוגיקה ורשת אספקת מתח צפופה במיוחד. לפי הדוברים, ניתוח IR-drop שטוח ברמת פול-צ’יפ לתכנון כזה דורש בדרך-כלל אלפי ליבות CPU, מאות טרה־בייט זיכרון ושבעה ימי ריצה לכל הרצה – פרקטיקה שמגבילה מאוד את מספר התרחישים (corners, עומסים, מצבי עבודה) שאפשר לבדוק בזמן הפיתוח.

המעבר ל-2.5D ול-3DIC מוסיף שכבה נוספת של מורכבות: אי-אפשר עוד להסתפק בניתוח השבב בלבד. יש תלות חזקה בין ה-die, האינטרפוזר והחבילה, כך שכל שינוי ברשת ההספק או בהוספת קבלי ייצוב במארז משפיע ישירות על ה-IR-drop על גבי השבב. הצורך, כפי שתואר, הוא בפתרון שמאפשר ניתוח מקבילי של die + אינטרפוזר + חבילה, בלי לשרוף שבוע לכל ריצה.

הפתרון שהוצג מבוסס על זרימת ניתוח היררכית עם מודלים מצומצמים – Reduced Order Models (ROM). בשלב הראשון מפיקים לכל בלוק היררכי בשבב מודל מופשט שמייצג את התנהגות רשת ההספק שלו על שכבת חיבור משותפת (roll-up layer). המודלים הללו, שאפשר להכין בכמה וריאנטים עבור תרחישים שונים, מחליפים את הגיאומטריה המלאה של שכבות המתכת הנמוכות באותו בלוק. ברמת הטופ-לבל מחברים רק את מודלי ה-ROM, בעוד שהאינטרפוזר והחבילה נשארים במודל מפורט.

במקרה המבחן שתואר – מאיץ ה-AI על גבי אינטרפוזר אורגני – נעשה שימוש ב-ROM עבור כל בלוקי ה-die (100% ROM), בעוד שהאינטרפוזר והחבילה נותחו במלואם. התוצאה: מספר ה"נודים" בסימולציה ירד ב-98.9% לעומת ניתוח פול-צ’יפ שטוח, זמן הריצה התקצר ב-86% (מכשבעה ימים לכיום אחד), וסך הזיכרון הפיזי שנדרש ירד ב-89%. הקטנה כזו של משאבי החומרה מאפשרת להריץ הרבה יותר וריאציות של העיצוב – זוויות PVT שונות, דפוסי עומס, תצורות רשת הספק – במסגרת אותו תקציב זמן ומחשוב.

כמובן, השאלה הקריטית היא מידת הדיוק. לפי התוצאות שהוצגו, ההבדלים ב-IR-drop בין הריצה ההיררכית לבין הריצה השטוחה המלאה נמצאו בטווח של מיליוולטים בודדים – הן על גבי השבב בלבד והן עבור המבנה המלא של die + אינטרפוזר + חבילה. במקרים רבים המודל המצומצם אף נטה להיות מעט פסימי, מה שמגדיל את מרווח הביטחון בתכנון ולא מסתיר בעיות.

לסיכום ציינו AWS ואנסיס כי השיטה ההיררכית מאפשרת לקבל זמן תגובה מהיר יותר, כיסוי רחב יותר ותשתית מחשוב זולה יותר – שלושה פרמטרים קריטיים בעידן שבו מאיצי AI בעלי מיליארדי טרנזיסטורים ואריזות 2.5D/3D הופכים לסטנדרט. לדבריהם, הזרימה החדשה כבר משולבת בפרויקטים נוספים, וצפויה להפוך לכלי מרכזי בדרישות ה-sign-off של מערכות-על שבב בדורות התהליך הבאים.