מומחה הווריפיקציה לורו ריזאטי ראיין לאחרונה את ז'אן-מארי ברונט (Jean-Marie Brunet), מנהל השיווק הבכיר בחטיבת פתרונות Scalable Verification (SVSD) של Siemens EDA כדי להבין טוב יותר את החשיבות של אומדן הספק מדויק ואופטימיזציה לתכנון מערכת על שבב (SoC) .

מה הבעיה העומדת בפני תעשיית המוליכים למחצה כיום ביחס לאומדן הספק לפני יצור סיליקון?

הבעיה היא הפער בין צריכת חשמל דינמית משוערת בתכנוניSoC לפני יצור הסיליקון לבין הספק בפועל שמופץ על ידי ה- SoC המיוצר. במהלך השנים האחרונות, לקוחות שמו לב שכאשר חוברו SoCs שתוכננו לאחרונה לשקעי מוצרי הקצה, צריכת החשמל הדינמית בפועל חרגה בסדר גודל מההספק המשוער.

זה נהיה קריטי לחזות במדויק את צריכת החשמל האמיתית תוך תכנון ואימות תכנונים חדשים.

הגורם העיקרי לפער הוא המעבר מטכנולוגיית CMOS מישורית מסורתית לטכנולוגיית FinFET . מבחינה היסטורית, טכנולוגיית ה– CMOS המסורתית סבלה מדליפת המתנה או זרם סטטי משמעותית. כשעבר לצמתים נמוכים יותר, הספקת ל -32 ננומטר, זרם ההמתנה גדל באופן אקספוננציאלי והיה בלתי ניתן לניהול. טכנולוגיית FinFET הורידה באופן דרסטי את הזרם הסטטי. אך למרבה הצער, זה לא שינה משמעותית את המיתוג או את הזרם הדינמי.

האם אתה יכול להרחיב מעט על פיזור הספק דינמי ב- FinFETs ?

טרנזיסטור FinFET מקל באופן דרסטי על דליפת החשמל של מכשירים מישוריים באמצעות גישה תלת מימדית. על ידי הרמת התעלה ועטיפת השער סביבו, המבנה המתקבל מספק בקרת תעלה יעילה יותר המפחיתה את הספק הסף והאספקה (איור 1).

Emulation-Centric Power Analysis of SoC Designs_Figure 1איור 1: התרשים מדגיש את קיבול שער FinFET בהשוואה לתהליכים מישוריים. (מקור (Cavium Networks

ב FinFETs- צריכת החשמל הדינמית מהווה את מרבית פיזור ההספק הכולל בגלל קיבולי סיכה גבוהים יותר בהשוואה לטרנזיסטורים מישוריים. התוצאה היא מספרי הספק דינמיים גבוהים יותר.

תכנון בטכנולוגיית FinFET דורש כללי תכנון מחמירים יותר שלוקחים בחשבון את דרישות תהליך. FinFET הכללים החדשים מרסנים סינתזה, מיקום, Floor Plan ואופטימיזציה המשפיעים על מדדי התכנון.

ניתוח החשמל ברמה של RTL הוא כעת חובה, עליו להתחיל מוקדם בזרימת התכנון ולהתבצע בכל שלבי זרימת התכנון, במקביל למדדי תכנון אחרים, כגון ביצועים ושטח. בדיקה צולבת בין RTL קוד תוכנה משובץ ופריסה חיונית בכדי לזהות ולפתור באגים בבעיות מוקדמות בתהליך התכנון.

אילו בעיות נוספות תורמות לפער בין צריכת חשמל דינמית מוערכת לפני סיליקון?

נושא חשוב נוסף נובע מהמגבלות הפנימיות של הגירוי המפעיל את התכנון הנבדק (DUT) במהלך אימות התכנון לפני הסיליקון.

כיום, תעשיית האלקטרוניקה עושה שימוש רב בציוני אמת כדי לאמוד ביצועים וצריכת חשמל של תכנונים חדשים. פלחי תעשייה שונים משתמשים בסוגים שונים של אמות מידה.

בתעשיית המובייל, מדד פופולרי מאוד בשם AnTuTu מעריך את הביצועים/ הספק של מכשירי סמארטפון וטאבלט. בענף הבינה המלאכותית/לימוד מכונה (AI / ML), חבילת הבדיקות של MLPerf מודדת ביצועים/עוצמה של מסגרות תוכנה של , ML מאיצי חומרה של ML ופלטפורמות ענן של . ML זה פופולרי הן לאימונים והן למסקנות. באחסון, מדידת IOPs מספקת הערכה מדויקת של ביצועים/דיוק למכשירים חדשים.

חובה להריץ אמות מידה אלה באימות טרום סיליקון. הראות המלאה בתכנון יכולה לזהות אזורים של צריכת חשמל מוגזמת לפני ייצור הסיליקון ולאפשר תיקוני תכנון.

כיצד מודדים את צריכת החשמל באימות טרום סיליקון?

באופן מסורתי, צריכת החשמל הושגה ברמת השער על ידי מעקב אחר פעילות המיתוג של ה- DUT המופעלת באמצעות ספסלי בדיקה המורכבים מווקטורי רגרסיה. לגישה זו יש שתי בעיות.

ראשית, הבדיקה מתרחשת מאוחר מאוד במחזור התכנון. למרות שהפער עם הסיליקון נמצא בטווח של %5 בלבד, אין מספיק גמישות כדי לתקן את הבעיה בתכנון. פשרה טובה יותר היא הערכת צריכת חשמל דינמית ב- RTL שמובילה לסטייה גדולה יותר מהסיליקון במגרש הכדורים של %15, אך מספקת גמישות גבוהה יותר לתמיכה בשינויים בתכנון.

שנית, וקטורי ספסל הבדיקה אינם מהווים ייצוג טוב לאופן השימוש בתכנון. כדי להשיג אומדן הספק מדויק, חשוב לתפוס את פעילות המיתוג בצורה מדויקת ככל האפשר בהקשר של מערכת היעד המפעילה עומסי עבודה אמיתיים וציוני ביצועים/הספק, כמתואר קודם.

מה ההגדרה לביצוע ניתוחי חשמל, וכיצד משיגים אותה?

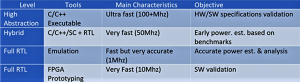

ברור כי הדמיית RTL אינה יכולה לבצע את העבודה התובענית יותר. מה שצריך זו גישה היררכית, המתחילה ברמה הגבוהה של הפשטה תכנונית בשלבים עד לרמת RTL ולמפלס השער. אין כלי אחד שיכול לעשות את העבודה כולה יותר. במקום זאת, כלים מרובים עם פשרות אופטימליות של מאפיינים יכולים להאיץ את הערכת החשמל ואופטימיזציה (ראה טבלה 1 להלן).

טבלה 1: גישה היררכית להערכת חשמל וניתוח הכרחית כדי להאיץ את התהליך. (מקור: לורו ריזאטי)

בשלב הראשון, כל ה- DUT המתואר ב- C/C ++ ברמת הפשטה גבוהה מאומת במהירות על פי מפרט חומרה/תוכנה, ונאמדת צריכת חשמל גסה מאוד.

בשלב הבא, תוקף פיזור הכח במערך היברידי המורכב מחלק תכנון המתואר ברמה גבוהה של הפשטה, כולל בדרך כלל ליבות וזיכרונות עיבוד כגון Arm Fast Models, וחלק התכנון האחר ב- RTL. החלק הגבוה של הפשטה מופעל על שרת מארח, ה- RTL מבוצע על ידי אמולטור חומרה, והשניים מחוברים באמצעות ממשק מבוסס טרנזקציות.

בעוד שהאמולטור פועל במהירות של מעט מאוד מגה-הרץ, התצורה ההיברידית עשויה להשיג מהירויות במגרש הכדור של 50 מגה-הרץ – מספיק מהר כדי לאתחל במהירות את אנדרואיד, לינוקס ואת כל הגרעינים שמתחת, כמו גם לבצע ניסוי ביצועים בתנאי מעבדה ובחיים האמיתיים.

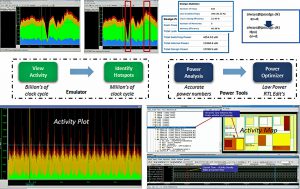

ההתקנה מספקת התחלה ראשונית לפרופיל התכנון כולו לצריכת חשמל בזמן קצר יחסית. על ידי תכנון פעילות המיתוג בטווח ארוך של מיליארדי מחזורי שעון, צוות התכנון יכול לזהות נקודות חמות של פיזור הספק גבוה ונמוך בטווחים של כמה מיליוני מחזורי שעון. באופן דומה, על ידי אזורי פיזור חשמל במפת פעילות, הצוות יכול לזהות חזותית קטעי תכנון של פיזור הספק גבוה ונמוך.

לאחר איתור נקודה חמה ואריחים קריטיים, הצוות יכול לעבור ל- RTL מלא וליהנות ממראות מדויקת ומפורטת בכל רשת תכנון. על ידי מתאם בין תאור הפעילות לקוד התוכנה המוטמע, כמו גם למפת הפעילות לקוד ה- RTL, הצוות יכול להתקרב במהירות לאזורים עם בעיות חשמל אפשריות.

חשוב ביותר לתפוס את פעילות התכנון המלאה לכל עיבוד עומסי העבודה, ולהימנע מדגימה, אשר נעשית בדרך כלל בפלטפורמות מבוססות FPGA אשר חסרות נראות פנימית מלאה (איור 2).

איור 2: כלים חשמליים יכולים לעקוב אחר ניתוח מגמות הספק בעזרת מפות ותיאור פעילות. (מקור: סימנס EDA)

ראוי להזכיר שבחברת שבבים גדולה היה שינוי בפרופיל המתח מוקדם ב- RTL לאחר שנוכחו בחיסול מדד Angry Birds באחד ממחשבי ה- SoC שלה שפועל על אמולטור. למען האמת זה היה די מגוחך לגלות שבתי מבדרת את עצמה כשהיא מפעילה את ישום ה- Angry Birds במכשיר ה- iPod שלה, וחברת השבבים הגדולה הזו מפעילה את אותה תוכנית על אמולטור.

לאילו התפתחויות אתה צופה בהמשך?

היבט תכנוני חדשני שמורכב מאוד לניהול בשלב טרום הסיליקון מתייחס לתכנוני Chiplets, Die Stacking, ו- 3D IC packaging .

הדיון הקודם שלי בנושא פרופיל הספק וניתוח התבסס על תכנון מונוליטי שבו כל הרכיבים משולבים על תבנית אחת. מה שאנחנו בוחנים בהמשך הם תכנונים המיושמים בחבילה מורכבת של IC. ברבים מתכנונים אלה, ליבות המעבד נמצאות על משטח אחד, ליבות ה- GPU על השנייה, זיכרונות על שלישית וכן הלאה, והן מתקשרות ביניהן באמצעות מצע או גשר מקושר לחיבור רב-מוטבע (איור 3).

איור 3: גשר אינטראקטיבי רב-מוטבע (EMIB) מאפשר תקשורת בין ליבות מעבד באחת, ליבות GPU באחרת וזיכרונות בשלישית. (מקור: אינטל)

ביצוע פרופיל וניתוחי מתח, כמו גם ניתוח תרמי בהיררכיית החומרה התכנונית ובמערמת התוכנה המשובצת הניתנת להגדרה המפוזרת על פני מספר תבניות היא מורכבת ומאתגרת.

עלינו לחשוב על הידור מודולרי והיררכי של תכנון שלם המכוון לפלטפורמת הדמיית חומרה ספציפית, ולתכנן את היכולת לגלוש, לזהות ולפתור באגים על פעילות מבוססת חומרה/תוכנה דרך ההיררכיה התכנונית.