בסימפוזיון הטכנולוגי של TSMC שנערך לאחרונה באמסטרדם חשפה החברה פרטים חדשים על טכנולוגית 16A וגם על טכנולוגית N2 * ד"ר קווין ז'אנג, סגן נשיא בכיר לפיתוח עסקי של TSMC עונה לשאלות CHIPORTAL אודות החידושים הטכנולוגיים

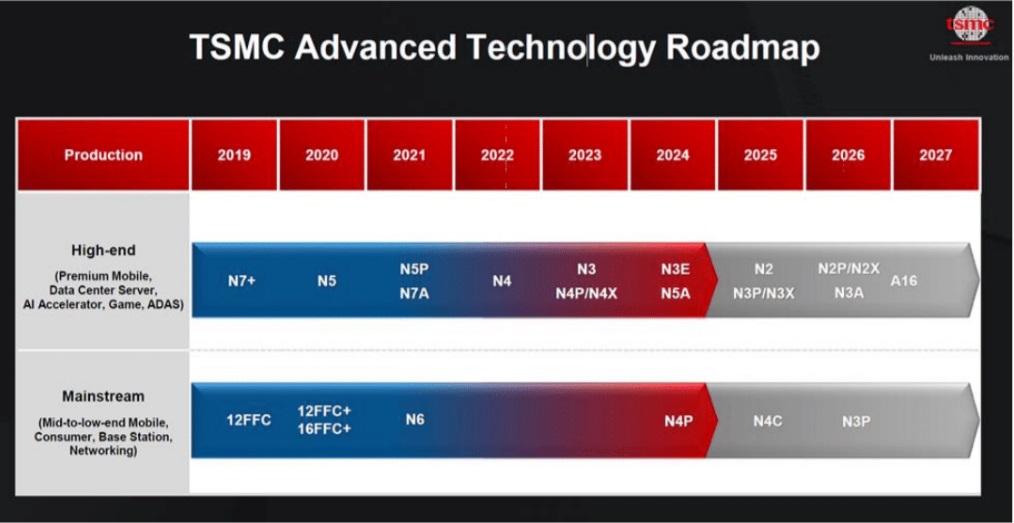

במהלך הסימפוזיון הטכנולוגי של TSMC שהתקיים באמסטרדם ב-14 במאי 2024, הציגה החברה את מפת הדרכים הטכנולוגית שלה, כאשר גולת הכותרת היא טכנולוגית 16A – כלומר צומת תהליך ברוחב 16 אנגסטרום או 1.6 ננומטר. ד"ר קווין ז'אנג, סגן נשיא בכיר לפיתוח עסקי של TSMC ענה לשאלות העיתונאים האירופים ובהם גם עורך CHIPORTAL אודות החידושים הטכנולוגיים.

מהי ארכיטקטורת Super Power Rail

"16A משלבת את ארכיטקטורת ה-Super Power Rail של TSMC עם טרנזיסטורים מסוג nanosheet, ומיועדת לייצור בשנת 2026. חידוש זה מביא לשיפור משמעותי בצפיפות הלוגיקה והביצועים."

"אחד המרכיבים המרכזיים בטכנולוגיית 16A הוא ארכיטקטורת ה-Super Power Rail. ארכיטקטורה זו מאפשרת ניתוב משאבי אספקת הכוח מאחור, מה שמפנה מקום לניתוב אותות בחזית השבב. בכך, היא מספקת שיפור בצפיפות הלוגיקה והביצועים של השבב. בהשוואה לתהליך N2P של TSMC, טכנולוגיית 16A תספק שיפור במהירות של 8-10% באותו מתח אספקת כוח (Vdd), הפחתת צריכת כוח של 15-20% באותה מהירות, ושיפור בצפיפות השבב של עד 1.10X עבור מוצרי מרכזי נתונים."

חדשנות NanoFlex לטרנזיסטורי nanosheet

בנוסף, טכנולוגיית N2 הקרובה של TSMC תכלול את TSMC NanoFlex, פריצה נוספת באופטימיזציה של תכנון-טכנולוגיה. TSMC NanoFlex מספקת למעצבים גמישות בתאי הסטנדרט של N2, אבני הבניין הבסיסיות של תכנון שבבים, עם תאים קצרים המדגישים שטח קטן ויעילות כוח גבוהה יותר, ותאים גבוהים הממקסמים ביצועים. היכולת לשלב תאים קצרים וגבוהים באותו בלוק תכנון מאפשרת ללקוחות לאזן באופן אופטימלי בין כוח, ביצועים ושטח בהתאם ליישום.

טכנולוגיית N4C

TSMC הכריזה גם על טכנולוגיית N4C, המהווה הרחבה של טכנולוגיית N4P. טכנולוגיה זו מציעה הפחתה בעלות המתה של עד 8.5% ומאמץ נמוך לאימוץ, ומתוכננת לייצור בכמות ב-2025. N4C מספקת IP יסודיים יעילים בשטח וכללי תכנון התואמים לחלוטין ל-N4P הנפוצה, עם שיפור בתשואה מהפחתת גודל הצומת, מה שמספק אפשרות חסכונית למוצרים ברמת ערך לעבור לטכנולוגיית מתקדמת הבאה מ-TSMC.

טכנולוגיית System-on-Wafer (SoW)

טכנולוגיית System-on-Wafer (TSMC-SoW) מספקת אפשרות חדשה מהפכנית לאפשר מערך גדול של מתים על וייפר בגודל 300 מ"מ, המציעים כוח חישוב רב תוך תפיסת שטח פחות משמעותי במרכזי נתונים והגברת ביצועים לכל ואט בהפרשים גדולים. ההצעה הראשונה של SoW מבוססת על טכנולוגיית Integrated Fan-Out (InFO) ונמצאת כבר בייצור. גרסה עם שבבים על וייפר המשלבת את טכנולוגיית CoWoS מתוכננת להיות מוכנה ב-2027, מה שמאפשר אינטגרציה של SoIC, HBM ורכיבים נוספים ליצירת מערכת ברמת וייפר עם כוח חישוב המשתווה לשרת מרכז נתונים או אפילו שרת שלם.

אינטגרציה של סיליקון פוטוניקס

TSMC מפתחת את טכנולוגיית Compact Universal Photonic Engine (COUPE) כדי לתמוך בגידול הנפיץ בהעברת נתונים הנלווה לגידול בתחום ה-AI. COUPE משתמשת בטכנולוגיית ערימת שבבים SoIC-X כדי לערום שבב אלקטרוני מעל שבב פוטוני, ומציעה את ההתנגדות הנמוכה ביותר בממשק שבב לשבב ויעילות אנרגטית גבוהה יותר משיטות ערימה מסורתיות. TSMC מתכננת לאשר את COUPE לחיבורים קטנים ב-2025, ולאחר מכן לשלב אותו באריזות CoWoS כאופטיקה משולבת באריזה (CPO) ב-2026.

ד"ר קווין ז'אנג, סגן נשיא בכיר לפיתוח עסקי של TSMC ענה לשאלות העיתונאים בכנס ובהם נציג CHIPORTAL אודות החידושים הטכנולוגיים. בתשובה לשאלתנו אודות הכניסה של TSMC לתחום פוטוניקת הסיליקון אמר ז'אנג: "TSMC מפתחת טכנולוגית סיליקון פוטוניקס כבר מעל חמש שנים. שימוש בטכנולוגיית ערימת 3D משלב בין שבבי פוטוניקה ואלקטרוניקה בגורם צורה קטן, ויוצר מנוע אופטי המשולב עם חישוב לביצועים גבוהים אבל כעת הטכנולוגיה נכנסת למיינסטרים של השבב.

היתרון העיקרי של שינוי רוחב הננו-שיט לשיפור ביצועים או כוח. האם M2 שלכם תומך ביכולת זו?

תשובה: "כן, ניתן לשנות את רוחב הננו-שיט. השינוי ברוחב הננו-שיט משנה דברים רבים בטכנולוגיה לעומת טרנזיסטור פלנרי ישן. הטכנולוגיה שלנו מספקת גמישות ללקוחות התכנון לשנות את רוחב השיט ולהתאים את גובה הספרייה. הטכנולוגיה "ננופלקס" מאפשרת ללקוחות לשנות את רוחב השיט ולשפר את ביצועי המוצר.:

מה התפוצה הנוכחית של ליתוגרפיה חישובית ב-TSMC וכיצד אתם מצפים שזה ישתנה עם מאיצי AI ולוגיקה חישובית?

"אנו משתמשים ב-CPU וב-GPU בשיתוף פעולה עם ספקי EDA לפיתוח ושיפור יכולות החישוב שלנו. יש לנו גם יכולות קנייניות רבות בתוך הבית."

מה היתרון של טכנולוגיית CPAP (Cfet) וכיצד היא תשפיע על הביצועים?

"CPAP מאפשרת בניית רכיבים עליונים זה על זה, מה שמאפשר הכפלת צפיפות הטרנזיסטורים ושיפור ביצועים. אנו גם חוקרים חומרים חדשים כמו חומרים דו-ממדיים לשיפור יעילות המעבר."

מהם השיפורים שאתם מצפים להשיג עם המעבר לשימוש בחומרים חדשים למעברי חשמל בתוך השבבים?

"אנו מחפשים חומרים חדשים לשכבת המוליכים בכדי להפחית את ההתנגדות ולשפר את הביצועים. שילוב של חומרים בעלי התנגדות נמוכה וקיבול נמוך ישפר את ביצועי השבבים."

מה הן היתרונות של אריזות מתקדמות לאוטומוטיב וכיצד הן משפרות את הביצועים?

תשובה: אריזות מתקדמות מאפשרות גמישות רבה יותר בתכנון השבבים ומתאימות למגוון רחב ל מוצרים. אנו משלבים טכנולוגיות כמו InFO ו-CoWoS כדי לשפר את ביצועי השבבים ברכבים.

האם יש תוכניות להרחבת יכולות האריזה המתקדמת של TSMC באירופה?

"כרגע אנו מתמקדים בהרחבת היכולות של היצור שלנו. אנו בוחנים אפשרויות שונות בשיתוף פעולה עם לקוחותינו, אך אין לי מידע ספציפי לשתף בנושא זה כרגע."

האם מפעלי הייצור החדשים של TSMC יתאימו לטכנולוגיות EUV ו-high NA?

" אנו לוקחים בחשבון את הצרכים העתידיים בעיצוב המפעלים שלנו. הטכנולוגיה high NA EUV תלויה באיזון אופטימלי בין עלות וביצועים."

כיצד טכנולוגיית ה-16A משפיעה על ניהול החום וביצועים תרמיים?

תשובה: שימוש בקשרי חשמל אחוריים דורש דקיקת הסיליקון, מה שעלול ליצור בעיות חום. אנו מפתחים שיטות להפחתת חום ונעבוד עם לקוחותינו על פתרונות קירור תרמיים מתקדמים.

כיצד תשפיע המעבר ל-A16 על הקטנת ההוצאות ללקוחות TSMC?

"טכנולוגיית ה-A16 משפרת את יעילות האנרגיה והביצועים, מה שמפחית את העלויות של הלקוחות שלנו. אנו שואפים תמיד להציע טכנולוגיה שתאפשר ללקוחותינו להפיק ערך מוסף ולמכור אותו ללקוחותיהם."

האם יש השפעה על TSMC מהרגולציות החדשות על ייבוא ציוד טכנולוגי לסין?

"נכון לעכשיו, איני מודע להשפעה כלשהי עלינו מהרגולציות החדשות."

,

גודל הצומת. טעות הקלדה