פלטפורמת Synopsys Discovery VIP מזרזת ומפשטת את האימות של רוב התכנונים המורכבים של מערכת על גבי שבב (SoC)

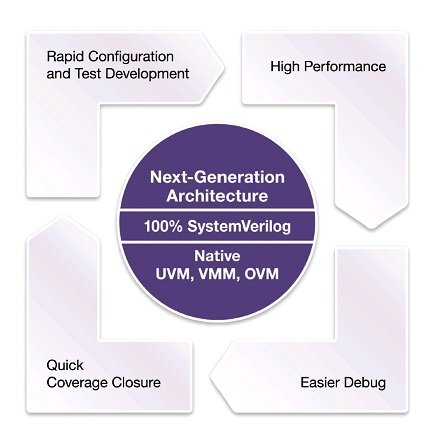

סינופסיס חשפה את משפחת המוצרים Discovery Verification IP (VIP), המבוססת על ארכיטקטורת VIPER. פלטפורמת Synopsys Discovery VIP כתובה כולה ב-System Verilog וכוללת תמיכה מובנית ב-UVM, VMM ו-OVM. הפלטפורמה מספקת ביצועים מובנים, קלות שימוש ויכולת הרחבה לזירוז ולפישוט אימות תכנוני מערכת על גבי שבב מהמורכבים ביותר.

ב-Synopsys Discovery VIP נכלל Protocol Analyzer, סביבה אימות (Debug) המודעת לפרוטוקול. פלטפורמת Discovery VIP תומכת בכל הסימולאטורים העיקריים ומציעה ביצועים בעוצמה של עד פי 4 לעומת מוצרי Verification IP מסחריים אחרים, וכן מציעה יכולות הגדרת תצורה, כיסוי ופיתוח בדיקות, בכדי לשפר את הקניין האינטלקטואלי ואת התפוקה של מתכנני מערכות על גבי שבב.

ארכיטקטורת ה-VIPER של הדור הבא מניחה את התשתית לחדשנות עתידית באימות מבוסס פרוטוקול ואימות ברמת מערכת על גבי שבב.

"אנו משתמשים ב-Synopsys VIP מזה כמה שנים ואנו מאוד מרוצים מהאיכות, הביצועים, הפונקציות והיכולות של הפלטפורמה", אמר ברוס פישביין, סגן נשיא בחטיבת הרשתות והתקשורת ב-Cavium. "ככל שהתכנונים וסביבות האימות שלנו מגיעים לרמות חדשות של מורכבות, החזון ומפת הדרכים מאחורי הארכיטקטורה של Discovery VIP יאפשרו לנו להתמודד עם הגל הבא של אתגרי אימות מערכות חומרה מורכבות על גבי שבב".

בעת שבה תכנונים מובילים של מערכת חומרה על גבי שבב כוללים פרוטוקולים מורכבים יותר, פלטפורמת VIP הפכה לרכיב קריטי בסביבת האימות, המאפשרת למהנדסים להגיע למטרות הכיסוי במסגרת לוחות זמנים צפופים בפרויקטים. פלטפורמת VIP מספקת מודלים פונקציונאליים של פרוטוקולים המצויים על גבי השבב ומחוץ לשבב, כגון ARM® AMBA®, PCI Express, USB, MIPI, HDMI ו-Ethernet. מהנדסי אימות עושים שימוש במודלים אלה כדי לבדוק את כל ממשקי ה-SoC לפני הייצור, מה שמאפשר אימות האם הממשק תואם את התקנים שפורסמו.

תמיכה מלאה ב-SystemVerilog ומימוש מובנה עבור -UVM, VMM ו-OVM

בשונה מפלטפורמות Verification IP אחרות, Discovery VIP כתובה כולה ב-SystemVerilog, בלי מעטפות או הרחבות מתודולוגיה סביב מימוש מקורי בשפה אחרת. פלטפורמת Discovery VIP בנויה עם תמיכה מובנית ב-UVM (Universal Verification Methodology), VMM (Verification Methodology Manual) ו-OVM (Open Verification Methodology) וכל זאת, ללא שימוש ב-מעטפות ברמת המתודולוגיה, בתרגומים סמויים או במיפוי מחדש. עובדה זו לא רק מסירה תקורה בלתי הכרחית של ביצועי יתר, אלא גם מציעה יתרונות מובנים ייחודיים אחרים. היתרונות כוללים ניידות לרוחב כל הסימולאטורים העיקריים ואינטגרציה קלה בתוך סביבות SoC. זאת בנוסף ליכולות ולפונקציות עבור אימות Verification IP וכן תכנון וניהול כיסוי.

"כמענה לצורך בשיפור בביצועים ויעילות צריכת החשמל, אנו רואים אימוץ רחב ומהיר בקרב התעשייה של הפרוטוקולים AMBA 4 AXI4™ ו- ACE™בכדי לתמוך במערכות חומרה על גבי שבב המאופיינות בעקביות פנימית, הטרוגניות וריבוי מעבדים", אמר וויליאם אורם, מנהל שיווק אסטרטגי בחטיבת המעבדים ב-ARM. "אנו תומכים בפיתוח ה- Verification IPעל ידי סינופסיס עבור הפרוטוקולים AMBA 4 AXI4™ ו- ACE™וסיפקנו מודלים לדוגמא עבור בדיקות תאימות ותאימות הדדית. אנו מצפים להמשיך לעבוד עם סינופסיס בצורה הדוקה בכדי לטפל בצרכים של לקוחותינו המשותפים".

תיקון שגיאות מודע-לפרוטוקול בעזרת Protocol Analyzer

בתקופה שבה הפרוטוקולים נעשים יותר ויותר מורכבים, תיקון ואימות שגיאות (debug) הפך לאחד ההיבטים הקשים וגוזלי הזמן ביותר באימות פונקציונאלי. ה-Protocol Analyzer של סינופסיס, אשר זמין במשפחת Discovery VIP, מספק כלי לתיקון שגיאות שהפרוטוקול עומד במרכזה, ויכולת הצגה (visibility) חכמה. יכולות אלה מאפשרות למהנדסים להבין במהירות את פעילות הפרוטוקול, לזהות צווארי בקבוק ולתקן שגיאות בהתנהגות שגויה של התכנון.

ארכיטקטורת VIPER

משפחת Discovery VIP מבוססת על ארכיטקטורת VIPER החדשה של סינופסיס, אשר תוכננה מהיסוד עבור ביצועי Verification IP משופרים, ועבור יכולת הגדרת תצורה, ניידות, תיקון שגיאות, ניהול כיסוי ותאימות, ויכולת הרחבה. רוב הפונקציונאליות של VIPER ויכולת בדיקת הנכונות הפרוטוקול (correctness) נובעת מארכיטקטורת פרוטוקול שכבתי מיישום ב-SystemVerilog, תוך שימוש בשיטות עבודה מומלצות עבור המתודולוגיות, כולל UVM, VMM ו-OVM. כל השכבות גלויות ונראות, דבר המספק יכולת שליטה מלאה באימות הפרוטוקול.

ארכיטקטורת VIPER מאפשרת לעקוב אחרי מידע סימולציה המבוסס פרוטוקול, כדי לספק תמונות מצב של ניתוח ברמת הפרוטוקול, מידע אשר כולל צירי זמן המסונכרנים לחומרה ולתמונות מצב אחרות. ניתן להגדיר באופן מלא את התצורה של ארכיטקטורה זו עבור תצורות פרוטוקול ספציפיות, והיא כוללת מספר יכולות כגון קיצוץ תצורות זמן ריצה לא רלבנטיות מרצף נתונים המוגדר מראש. ארכיטקטורת VIPER היא גם בעלת אפשרות הרחבה משמעותית, והיא כוללת בתוכה יכולות נוספות הייחודיות ל-Device Under Test (DUT), כגון אופנים לשיבוץ שגיאות, דגימות כיסוי ויכולות אחרות.

"אימות פרוטוקול הפך לחלק קריטי באימות מערכות על גבי שבב, ויש לו השלכות כבדות משקל על עלויות ועל זמן לשיווק", אמר מנוג' גנדי, סגן נשיא בכיר ומנהל בקבוצת האימות של סינופסיס. "סינופסיס זיהתה את הצורך בדור חדש של Verification IP בכדי לשפר את תיקון ואימות השגיאות, את הביצועים ואת קלות האינטגרציה של מערכות חומרה על גבי שבב. ההשקה של ארכיטקטורת הדור הבא של-Verification IP שלנו היא קריטית לתעשייה, בכדי להתמודד עם האתגרים הגוברים בתחום האימות של מערכות חומרה על גבי שבב".

| {loadposition content-related} |