מושב הפתיחה של כנס ChipEx2012 עסק בעתיד הבלתי נמנע של תעשיית השבבים – תלת ממד, מה שהיום התחיל כקטיף הפירות הנמוכים יהפוך בעתיד לזרם המרכזי. שלושה מרצים מוסרים את תחזיותיהם: פול פרנזון מאוני' צפון קרוליינה, אי ג'יי אינקורביה סגן נשיא למו"פ בחברת קיידנס, ואודי צורי – הCMO מנהל השיווק הראשי של אפלייד ישראל

| פרופ' פול פרנזון, אוני' צפון קרוליינה בכנס ChipEx2012. צילום: ניב קנטור |

מושב הפתיחה של כנס ChipEx2012 עסק בעתיד הבלתי נמנע של תעשיית השבבים – תלת ממד, מה שהיום התחיל כקטיף הפירות הנמוכים יהפוך בעתיד לזרם המרכזי. שלושה מרצים מוסרים את תחזיותיהם: פול פרנזון מאוני' צפון קרוליינה, אי ג'יי אינקורביה סגן נשיא למו"פ בחברת קיידנס, ואודי צורי – הCMO מנהל השיווק הראשי של אפלייד ישראל.

נקודת מבט טכנולוגית: פרופ' פול פרנזון מאוניברסיטת צפון קרוליינה, וגם אחד המומחים ב-3DIC.

"כבר היום ניתן למצא שבבים המיוצרים בטכנולוגית תלת ממד ובקרוב נראה עוד יותר.

היתרון העיקרי של תלת מימד הוא שהפלטפורמה מתוכננת ספציפית לתלת ממד. בטווח הקצר יבקשו החברות לקטוף את הפירות הנמוכים – בעיקר בתחום הזיכרונות. בטווח הבינוני לוגיקה על לוגיקה וזיכרון על לוגיקה, ובטווח הארוך אינטגרציה הטרוגנית – כלומר כל שכבה תספק רכיב אחר של המערכת, וכמובן מיזעור, כאשר יש להתגבר על מגבלת ההכשרה של העובדים."

"יש היום בתכנון חיישני תמונות, זיכרונות בעיקר לשרתים, בעתיד יהיו גם שבבי תלת מימד לתחום המובייל ואף מעבדים שלמים שיתוכננו וייוצרו בטכנולוגית תלת ממד. זה הולך לאט בעיקר בגלל עלות הייצור אך בעתיד נוכל לקבל טרה בייט של זיכרון על שבב אחד."

אז מה שונה בתכנון שבבים תלת מימדים?

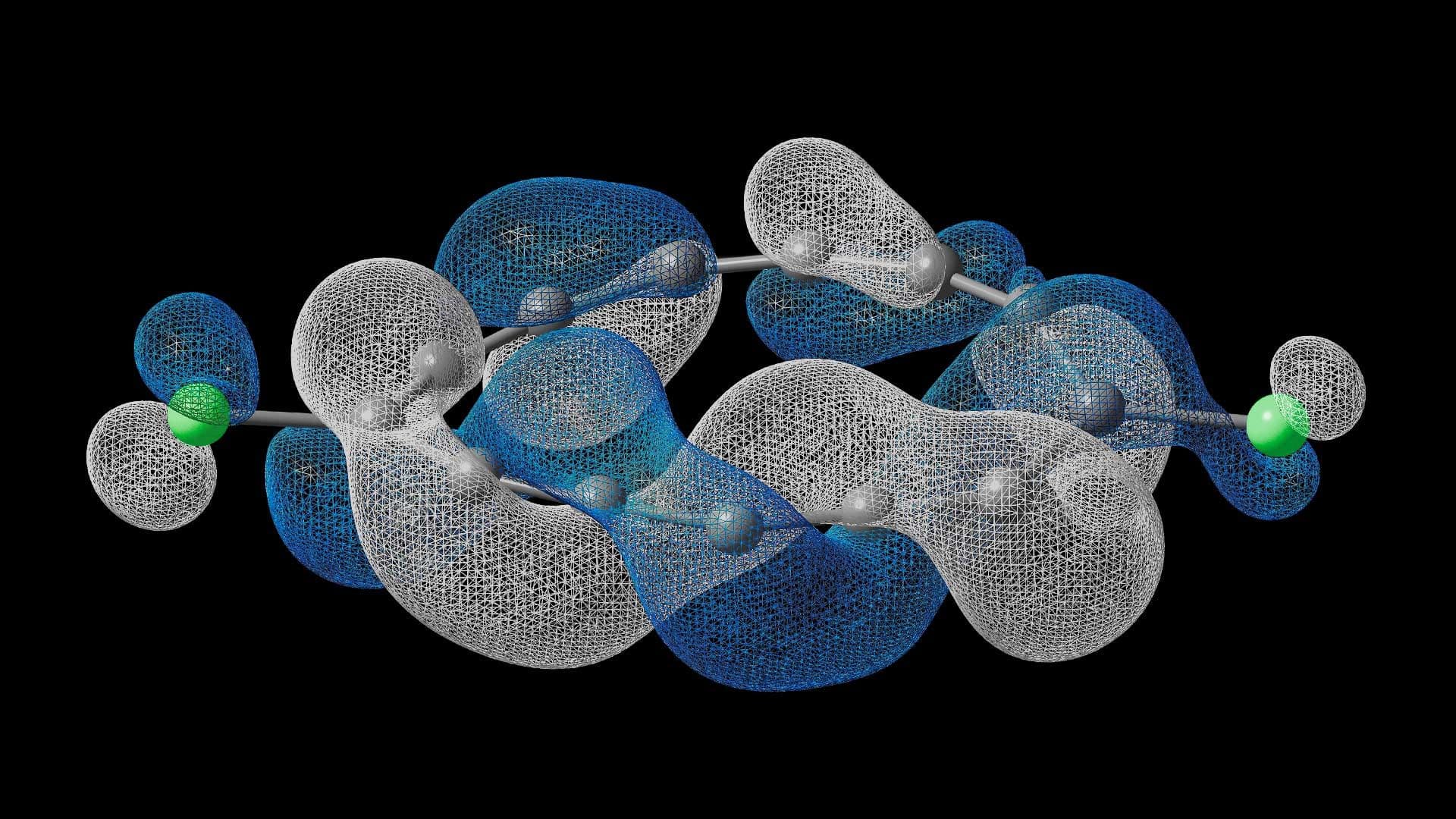

"זהו שילוב הטרוגני – כלומר כל שכבה של השבב היא שונה וזה מאפשר ביצועים טובים ויתרונות מחיר בעיקר ביישומים בהם חשובה מהירות העברת הנתונים. זה חשוב גם לתקשורת רחבת פס וגם לזיכרונות."

"בסופו של דבר 3DIC יאפשרו קיצור החוטים ובכך ייחסך חשמל ויופחתו הלעלויות. ממשק הזיכרון הוא המקור הגדול ביותר לסבך כבלים ארוכים. באשר לשילוב ההטרוגני – כל שכבה תהיה שונה, ובהינתן היתרונות בביצועים ובעלויות, במיוחד ביישומים הדורשים חיבוריות גבוהה. היעד הוא להגיע ל"שבבי על" (super chips) ולהפחית את עלות האריזה, כמו גם לאפשר בניית מיקרו מערכות משולבות."

כמה מהטכנולוגיות הקיימות כיום כוללות:

• MEMORY ON LOGIC – מאפשר להתייחס לכל שכבה כזיכרון בודד וע"י זה נותן עוד גמישות על המעבד. זה טוב לתחום המובייל שם חשובה קיבולת הנתונים אך יש מגבלות אנרגיה.

• שיטה נוספת משתמשת ב DARK SILICON. במקרה הזה מרבית הזיכרון יהיה כבוי כאשר הוא אינו בשימוש.

• יש עבודה גם עבור ישומים צבאיים כמו למשל מכ"מ סינטטי.

•

"אני מאמין כי נראה את זה גם בתחום החיישנים שם חשובים מאד הגודל וצריכת האנרגיה.

וכן בתחום ה – RFID המשמש לניטור איכות מזון וישומים אחרים המסתייעים בתקשורת טווח קצר."

לסיכום, אומר פרופ' פרנזון כי המגבלות להטמעה הטכנולוגיה בטווח הקצר קשורות בנושא התרמי. יש צורך בבידוד תרמי של הזיכרון וכן בכמה בעיות אינהרננטיות לסביבה:

• TEST – המורכבות של הבדיקות עולה

• CODESIGN – יש לשנות את ממשקי ה-CAD

• COST AND YIELD יש צורך בתמיכה בהורדת עלויות ייצור באמצעות התכנון

נקודת מבט באמצעות כלי תכנון לתלת ממד. אי ג'יי אינקורביה סגן נשיא למו"פ בחברת קיידנס

אי ג'יי אינקורביה סגן נשיא למו"פ בחברת קיידנס. צילום: ניב קנטור

"לא יפתיע אף אחד אם אומר כשכאשר אנחנו עוברים לגדלי NODE קטנים יותר יש גידול דרמטי בעלות וביכולת שלנו לעבוד בטווחים אלה. שימוש ב-TSV ( Through Silicon Vias) היא דרך אחת לעקוף כמה מהאתגרים. מעבר לערימה אנכית תוך שימוש ב-TVS יאפשר שימוש חדש ב-NODE ישנים יותר (בעיקר ב-IP ובשילוב ההטרוגני), יגדיל את הביצועים ויפחית את צריכת החשמל ועלות הייצור."

"טכנולוגית שבבים בשכבות איננה דבר חדש אבל כעת נדרש שינוי פרדיגמה מ-SOC דו ממדיים לשכבות תלת מימדיות. הסיבה לכך היא הגדלת ביצועים הורדת צריכת החשמל ובעתיד גם הפחתת עלויות. בשוק ה-FPGA יש כבר מוצר ראשוני בתלת ממד, וגם אלטרה תוציא לשוק מוצר בתלת מימד. בתחום הזיכרון – מיקרון תכריז על שבב שיהיה בשנה הבאה. בשלב הבא נראה לוגיקה פלוס זיכרון על SILICON INTERPOSER בעתיד גם אנו נחזה ב- WIDE AREA I/O בשבבים למחשבים עתירי ביצועים."

"אנחנו בקיידנס, מספקים כלי EDA כדי לתמוך בפיתוחים הללו ועובדים בשיתוף עם המפעלים, חברות הבדיקות וקהילת התכנון כי יש קשר הדוק בין מה שבעבר נעשה בחברת אריזת השבבים למה שנעשה כיום במפעל. צריך לעבוד עם שותפי האקוסיסטמם משלב התכנון כדי לדעת באילו טכנולוגיות ישתמשו."

"קיידנס גם עובדת בשיתוף פעולה עם TSMC כדי שהתכנון שלנו יוכל לתמוך בזרימת התהליך של TSMC. החברה מאפשרת היום פיתוח של טייפאאוטים מרובי שבבים תלת ממדיים לרבות שבבי זיכרון על לוגיקה בטכנולגית 28 ננומטר, לוגיקה על גבי אנלוג,לוגיקה על לוגיקה, ו-DIE בעלי שלוש שכבות, וכן היא מאפשרת הכנת טייפאאוטים לתכנון הייצור."

"לסיכום אומר אינקורביה: החדשות הטובות הן שתכנון ל-3DIC אינו טריוויאלי, יש עוד עבודה לעשות אבל יש כלים בשוק המאפשרים לכם להתחיל לעבוד בתחום התלת מימד. "

נקודת מבט יצורית: אפלייד מטיריאלס יצרנית כלים ליצרני IC. האתגרים של D-IC3 הם בצד הייצור. אודי צורי – הCMO מנהל השיווק הראשי של אפלייד ישראל.

אודי צורי – הCMO מנהל השיווק הראשי של אפלייד ישראל. צילום: ניב קנטור

"עד כה רוב הדיבורים היו על האריזה של השבב. אני אדבר על רמת הייצור של השבב הבודד, אשלים את התמונה בנשוא ואכסה את עולם התלת מימד. אני צופה שבחמש השנים הקרובות יהיו יותר שינויים מהותיים בתעשיה מאשר היו ב-15 השנה האחרונות."

"ככל שיורדים לגיאומטריות של 20 ננומטר ופחות מזה צריך למצוא פתרונות רדיקאלים כדי להגיע לביצועים הצפויים. המהפיכה הגדולה היתה בתחום הליטוגרפיה מליטוגרפיה יבשה ל-IMMERSION ובעתיד ל-EUV. אנו חווים בימים אלה מעבר ממשטחי סילקון (ווייפרים) קטנים ליותר גדולים – המעבר הבא – ל-450 וכן מעבר ממבנים שטוחים ברמת הטרנזיסטור והזיכרון למבנים תלת ממדיים."

"ברמת הזיכרון – לפני שנתיים הציג מישהו מסמסונג – מעבר ל-Flash VERTICAL3D ואמר שזה יקרה באיזור ה-10 ננומטר ב-2023. המסר הוא שחברות כמו סמסונג וטושיבה נמצאות בתהליכים מאוד מתקדמים וביצוע ניסויים של זיכרונות תלת ממדיים. בשנה הקרובה נראה ייצור המוני עד 2015. הרבה יותר מהר ממה שסברו קודם. "

"הסיבה העיקרית להתפתחתו זו היא טכנולוגית ה-Extreme ultraviolet ) EUV ) ככל שמבינים שהכניסה של EUV רחוקה, מחפשים פתרונות אחרים להתגבר על הבעיות ואחד הדברים הוא המעבר לתלת ממד. "

"פלאש NAND ורטיקלי או תלת ממדי מיוצר כך שמקבלים את הזיכרון ומעמידים אותו לגובה וכך מרוויחים הרבה יותר שטח. כשהיתרונות הן חוסר התלות בליטוגרפיה ובצורך לצופף את הקווים כפי שהיה קודם. יש גם יתרונות בהורדת הCUPELING בין תאי הזיכרון ויש גם אפשרות לעשות Scalability לעלות. לבנות לגובה בלי להוריד את הDesign RULE."

"האתגרים בייצור – בניה של שכבות שכבות – כבר בהתחלה מדברים על 32 שכבות שמייצרים אותם באמצעות שיקוע. שכבות של חומרים שונים קשה מאוד לשלוט בממשק בין השכבות כשעושים את הדפוזיה בין השכבות. אין אפשרות לשלוט ברמת השכבה הבודדת. משתמשים באותם טכנולוגית יצור גם בדו-מימד וגם בתלת ממד, כמעט אותם חומרים הקושי הגדול הוא באינטגרציה בין התהליכים. והקושי הנוסף אולי הכי גדול זה ביכולת לשלוט בתהליכים השונים. כי צריך לבקר את התהליכים תוך כדי הייצור."

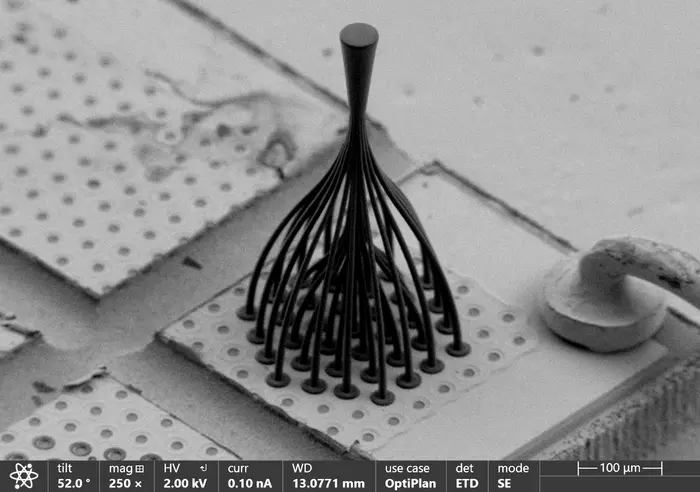

"בטרנזיסטורים – מרימים את ה-SOURCE והDRAIN- בצורת נפיר ומקיפים אותו מ-3 צדדים. הטכנולוגיה שתעזור היא זו שתשתמש במיקרוסקופ אלקטרונים E-beam. "

"לסיכום נושא התלת ממד ברמת הוויפר זה קורה הרבה יותר מהר ממה שחשבנו, יש כבר טרנזיסטורים תלת ממדיים וזיכרונות תלת מימדיים. עיקר האתגרים הם לא בייצור של השכבות הבודדות אלא באינטגרציה בין כל השכבות והמדידה שלהם ומציאת הפגמים תוך כדי הייצור. יש המון אתגרים שאין להם פתרונות ייצוריים ולפחות כיוון אחד שאנחנו בודקים הוא השימוש של EBEAM כדי לעשות הדמיה ומדידות של הטרנזיסטורים והזיכרונות על רמת הWAFER."

| {loadposition content-related} |