אינטל הכריזה לאחרונה על אסטרטטגית אריזה חדשה, הכוללת את טכנולוגיות Foveros ו-EMIB שלה, שואפת לחולל מהפכה בייצור השבבים על ידי אספקת פתרונות מהירים וחסכוניים יותר החורגים משיטות התכנון המסורתיות

שיטות ייצור שבבים מסורתיות מסתמכות מזה זמן רב על תבניות סיליקון גדולות ומונוליטיות שהגבילו את הפוטנציאל לחדשנות והתאמה אישית. ככל שהטכנולוגיה מתקדמת בקצב מהיר, יש צורך הולך וגובר בשינוי פרדיגמה בתעשייה כדי להתאים לדרישות המתפתחות ללא הרף של עסקים וצרכנים כאחד. אסטרטגיית האריזה המתקדמת של אינטל, הכוללת את טכנולוגיות Foveros ו-EMIB שלה, שואפת לחולל מהפכה בייצור השבבים על ידי אספקת פתרונות מהירים וחסכוניים יותר החורגים משיטות התכנון המסורתיות.

בשבוע שעבר התקיים תדרוך עיתונאים מקוון בהשתתפות טום רוקר, עמית אינטל ומנהל תחום מפת הדרכים של ההרכבה והבדיקות, פויה טאדאיון, מנהלת בכירה במחלקה לאריזה מתקדמת של הפאונדרי ותום גרדנר, מנהל בכיר באותה מחלקה.

טכנולוגיות האריזה החדשות: Foveros ו-EMIB

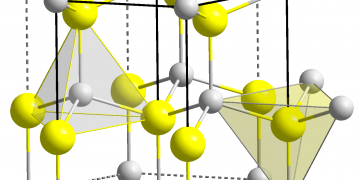

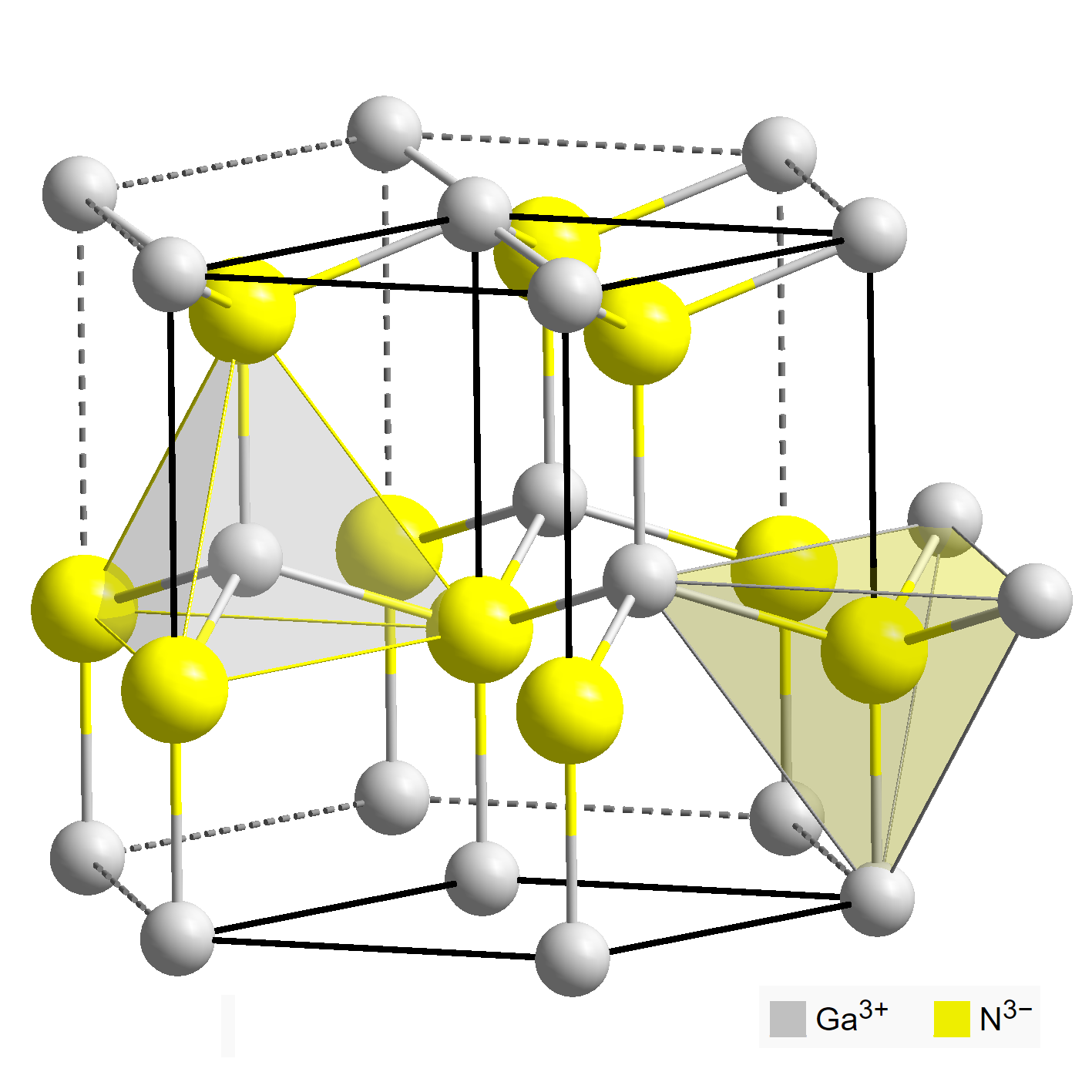

טכנולוגיית Foveros, שהוצגה לראשונה על ידי אינטל בשנת 2019, מבוססת על שכבת בסיס לוגית ראשונית, שעליה ניתן להתקין שכבות לוגיות נוספות, למשל רכיבי CPU או רכיבי FPGA, ועליהן שכבות נוספות כמו מעגל אנלוגי או זכרונות. השכבות מקושרות אחת עם השניה באמצעות מגעים כדוריים זעירים המקשרים את המודולים החשמליים של פיסות הסיליקון.

הטכנולוגיה הזו נועדה לספק מענה לרכיבים מסוג חדש (Chiplets) שבהם מספר פרוסות סיליקון נפרדות מקושרות ישירות אחת אל השנייה ומספקות פונקציונליות גדולה. לגישה הזאת יש מספר יתרונות מובנים: ניתן להגיע לצפיפות מעשית גדולה מאוד גם בלא מעבר לתהליכי ייצור מתקדמים ויקרים שבהם רוחב הצומת של הטרנזיסטור קטן מ-10 ננומטר.

הטכנולוגיה מאפשרת חיבורים בצפיפות גבוהה, וכתוצאה מכך קלט/תפוקה מוגברת, תפוקה גבוהה יותר ועלויות ייצור נמוכות יותר. טכנולוגיית Foveros Direct הקרובה תכלול חיבור ישיר מנחושת לנחושת עבור חיבורים בעלי צפיפות גבוהה והתנגדות נמוכה, ותציע את ביצועי הספק הסיביות הטובים ביותר.

טכנולוגיית EMIB (Embedded Multi-die Interconnect Bridge) היא מרכיב קריטי נוסף באסטרטגיית האריזה המתקדמת של אינטל. טכניקה זו מספקת חיבור חשמלי במהירות גבוהה בין שבבים הטרוגניים (לוגיקה, זיכרון וכו ') בתוך חבילה אחת, המאפשר ביצועים טובים יותר ויעילות אנרגטית. EMIB מאפשר לאינטל לשלב פונקציות שונות בטביעת רגל קטנה יותר, תוך הפחתת המורכבות והעלות הכוללת של המערכת.

הן Foveros והן EMIB מייצגות התקדמות משבשת בתחום ייצור השבבים, ומאתגרות שיטות מסורתיות המסתמכות על תבניות סיליקון מונוליטיות. טכנולוגיות אלה מאפשרות ל-Intel ליצור מוצרים רב-תכליתיים יותר הניתנים להתאמה אישית העונים על צרכי לקוחות ספציפיים תוך שמירה על עלויות, הספק וטביעות רגל פיזיות.

שינוי הפרדיגמה בייצור שבבים

טכנולוגיות האריזה המתקדמות של אינטל מייצגות שינוי משמעותי באופן הייצור והעיצוב. על-ידי שילוב יכולות נוספות בכל דור מוצרים חדש, אינטל יכולה להציע מגוון רחב של פתרונות המותאמים לדרישות ספציפיות של לקוחות. זהו שינוי ניכר משיטות הייצור המסורתיות המתקשות להתאים לצרכים והעדפות מגוונים.

שמירה על עלות, הספק וטביעת רגל פיזית הם שיקולים חיוניים בייצור שבבים. אסטרטגיית האריזה החדשה של אינטל מאפשרת לחברה להשיג יעדים אלה תוך אספקת מוצרים חדשניים ובעלי ביצועים גבוהים.

תכנון שבבים המותאמים לדרישות ספציפיות ללקוח הוא היבט מכריע נוסף של שינוי פרדיגמה זה. טכנולוגיות האריזה המתקדמות של אינטל מאפשרות יצירת פתרונות מותאמים אישית הנותנים מענה לשווקים ויישומים שונים, ומטפחים בידול ותחרותיות. כתוצאה מכך, לקוחות אינטל יכולים ליהנות מגמישות רבה יותר ומאפשרויות בחירה בבחירת תכונות, רכיבים וצמתי תהליך העונים על דרישות העיצוב הייחודיות שלהם.

אבני דרך מרכזיות והתפתחויות עתידיות

לאינטל יש כמה אבני דרך מרכזיות באופק שמציגות את מחויבותה למובילות מתקדמת בתחום האריזות. בשנת 2022, מעבדי Sapphire Rapids ופונטה וקיו שכוללים טכנולוגיות אלו, מייצגים את נפח המוצרים הגדול ביותר שאינטל משווקת. . בנוסף, בשנת 2023, אינטל תיערך לייצור של Meteor Lake, אשר צפוי להישלח ללקוחות בהיקף של מאות מיליוני יחידות תוך שימוש בחיי אריזת התלת-ממד המתקדמת האחרונה, Foveros.

מפת הדרכים עליה הכריזה אינטל מובילה לכך שאותן טכנולוגיות, כמו למשל: Flip Chip Ceramic, Flip Chip Organic & Multi Chip Pkg, 2.5D EMIB, 3D Foveros, 2.5D EMIB + 3D Foveros ו-3D Foveros Direct. תורמות למעמדה של אינטל בתעשייה.

כניסה לעסקי הפאונדרי עשויה להועיל משמעותית לעסקי המחשבים של אינטל. השתתפות בפעילות פאונדרי תעניק לאינטל קנה מידה שיסייע לדחות הוצאות הנדסיות והשקעה בעסק גדול בהרבה.

המובילות המתקדמת של אינטל בתחום האריזה נובעת משילוב של גורמים רבים, כולל צפיפות חיבורים, ניהול תרמי, ניהול צריכת חשמל וקלט/פלט במהירות גבוהה. על ידי השקעה אסטרטגית בהיבטים אלה, אינטל יכולה להמשיך להוביל את התעשייה בטכנולוגיות אריזה מתקדמות ולשמור על יתרון תחרותי בשוק ולייצר יתרון חדש בשוק הפאונדרי.

היתרונות המודולריים של טכנולוגיית האריזה של אינטל

טכנולוגיית האריזה של אינטל מציעה מספר יתרונות מודולריים, ובראשם המעבר ממערכת-על-שבב למערכת על אריזה. גישה זו מאפשרת את הגמישות של אריזת כתובות IP חיצוניות ופנימיות כדי לספק מוצרים מובילים. זה גם מאפשר עיצוב מוצר / אריחים להיות בשימוש חוזר בין מוצרים, מה שמוביל למבנה עלות שווה ערך או טוב יותר בהשוואה לעיצובים מונוליטיים.

דוגמה לייצור מודולרי זה בעבודה היא Intel Data Center GPU Max, המורכב מ-47 אריחים על פני חמישה צמתי תהליך ומכיל 100 מיליארד טרנזיסטורים. עיצוב חדשני זה מדגים כיצד טכנולוגיית האריזה המתקדמת של Intel מאפשרת בידול והתאמה אישית בשוק.

תרומתה של אינטל לחוק מור ולטריליון שבבי טרנזיסטורים

תפקידה של האריזה ותרומתה לסולם חוק מור מתפתח והופך לאחד הגורמים העיקריים המאפשרים השגת שבבי טריליון טרנזיסטורים עד סוף העשור. עד שנות ה-2010, הפונקציה העיקרית של האריזה הייתה ניתוב כוח ואיתות בין לוח האם לסיליקון תוך הגנה על הסיליקון עצמו. עם כניסתנו לעידן האריזות המתקדמות, אנו עוברים ממערכת-על-שבב למערכת שבב, שבה לאדריכלים ולמעצבים יש את הכלים הדרושים להם כדי להגדיל עוד יותר את מספר הטרנזיסטורים למכשיר באמצעות שילוב דו-ממדי ותלת-ממדי של שבבים.

טכנולוגיות אריזה חדשות, כגון שבבים מונוליטיים (QMC), מאפשרות לחבר שבבים בצפיפות וברוחב פס דומים לאלה הנמצאים בחיבורי מערכת-על-שבב מונוליטיים. זה מאפשר אינטגרציה קלה יותר מכיוון שמעגלי החיבור פשוטים הרבה יותר, מפחיתים תקורות הספק והשהיה כדי למקסם את ביצועי המערכת, ומציע גמישות רבה בשילוב טכנולוגיית השבבים הטובה ביותר עבור כל חלק במערכת (למשל, טכנולוגיות אופטימליות לעיבוד, זיכרון, אספקת חשמל וכו ').

EMIB ו-Foveros הן טכנולוגיות מובילות בתעשייה שכבר נשלחו בכמויות. פתרונות אלו מאפשרים לאינטל לשלב ולהתאים טכנולוגיות IP מובילות ותהליכי עיבוד ממקורות פנימיים וחיצוניים על גבי מוצר אחד על גבי מוצר. יתר על כן, גישה זו מאפשרת פילוח רחב ויעיל יותר כדי לענות על הצרכים הייחודיים של מגזרי מוצרים מרובים.

Universal Chiplet Interconnect Express (UCIe) Consortium

קונסורציום Universal Chiplet Interconnect Express (UCIe) הוא קבוצה של מובילי תעשייה שהתאחדו כדי לבנות סטנדרטים לעידן החדש של שבבים בעלי יכולת פעולה הדדית שיניעו את הדור הבא של חומרת המחשוב. טכנולוגיית UCIe היא תקן תעשייה פתוח שפותח כדי לקיים אינטראקציה בכל מקום ברמת החבילה תוך תגובה לבקשות לקוחות לשילוב ברמת החבילה הניתן להתאמה אישית.

אסטרטגיית האריזה של אינטל, הכוללת טכנולוגיות Foveros ו-EMIB, אמורה לדברי ראשיה להגדיר מחדש את ייצור השבבים על ידי אספקת פתרונות מהירים וחסכוניים יותר החורגים משיטות התכנון המסורתיות. "שינוי פרדיגמה זה מאפשר לאינטל לשלב יכולות נוספות בכל דור מוצרים חדש תוך שמירה על אותה עלות, הספק וטביעת רגל פיזית. יתר על כן, גישה זו מאפשרת שבבים המותאמים לדרישות ספציפיות ללקוח, ומטפחים בידול בשווקים שונים. ככל שאינטל תמשיך להוביל את התעשייה בטכנולוגיות אריזה מתקדמות, לחידושים שלה תהיה ללא ספק השפעה מתמשכת על מגזר ייצור השבבים ויעצבו את עתיד המחשוב."