איגור אלקנוביץ', CTO של חברת GUC – חברה בת של TSMC תיאר בכנס ChipEx221 את תחום אריזת השבבים, והסביר כיצד ערימה של שבבים זה לצד זה וזה מעל זה מאפשרת ביצוע של יישומים מתקדמים

מהפכת השבבים ה-2.5 והתלת ממדיים בעיצומה. כך מתאר ד"ר איגור אלקנוביץ', ה-CTO של חברת GUC בכנס ChipEx2021 שהתקיים לאחרונה בת"א על ידי חברת ASG. הוא הקדיש את הרצאתו לתחום אינטגרציה של Dies רבים זה לצד זה זה מעל זה. GUC היא חברה בת של TSMC. אנחנו משתמשים בטכנולוגיה של TSCMC ואחראים על כל הקשור לאריזה, ומפתחים את ה-IP הרלוונטי.

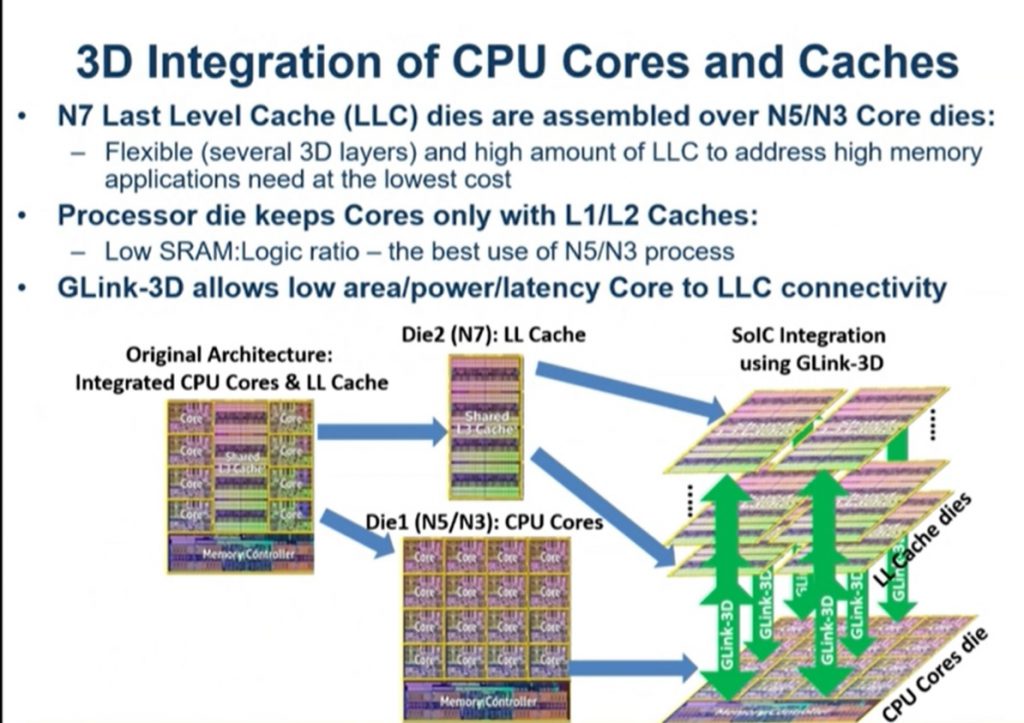

"אני מציג צורות שונות של אינטגרציה . אנו יוצאים מהאינטגרציה הבסיסית של הDIE למצע (MCM), וממשיכים אותה בחיבור ב-2.5 ממדים (Glink 2.5D for CoWoS/info_oS), דרך Glink-3D for Soic CoW/WoW וגם שילובים שלהם 3D ON 2.5D כלומר שכבות שונות של מספר שבבים שמחוברים זה לצד זה."

"אנחנו בונים את השרשרת ומשלימים בכך את התהליך של TSMC ומאפשרים לה להגיע לטכנולוגית 3 נונמטר כשבינתיים אנחנו מאפשרים להגדיל את ביצועי השבבים בטכנולוגית 7 ננומטר."

"אנחנו היינו הראשונים בתעשייה שמפתחים את היכולות האלה בזכות העובדה שאחנו חברה בת של TSMC ויש לנו גישה לטכנולוגיה. למעשה כבר בטכנולוגית 5 ננומטר אנחנו מאפשרים לעשות שימוש במצע ולקבל זמני תגובה של 5 ננו-שניות. זה חשוב ליישומים כמו מעבדים מרכזיים או מעבדי רשת."

בכל הקשור לזכרון SRAM, לדברי אלקנוביץ' התהליכים המתקדמים5 ו-3 ננומטר יאפשרו שיפור נוסף בצפיפות הלוגיקה, מהירות וצריכת אנרגיה ואולם SRAM יצבור פחות יתרונות במעבר ולפי החישובים, שבעה ננומטר זו הטכנולוגיה האופטימלית מבחינת עלות של SRAM. לפיכך הוא מציע להשתמש בטכנולוגיות 5 ו-3 ננומטר ללוגיקה (CPUs) ו-7 ננומטר לזכרון.

לסיכום אמר אלקנוביץ' כי SOIC (IC תלת ממדי) יגרום למהפכה בדרך שבה מתעננים מעבדים, שבבים גרפיים, מעבדים לHPC, בינה מלאכותית ומעבדי רשת. טכנולוגית Glink-2.5D מאפשרת אף היא שידרוג לחלק ממערכות ה-IP וכן החברה עדיין מציעה פתרונות מלאים ל-HBM לכל המעבדים מ-16 ננומטר ועד 5 ננומטר ובקרוב שלושה ננומטר. עד כה הוציאה החברה טייפאאוט ל112 אריזות GBPX .