בגליון זה יש לנו הכבוד והעונג לארח את ד"ר מרק ליו, יו"ר חברת TSMC

בימים אלו, תפקידה של תעשיית המוליכים למחצה, כטכנולוגיה בסיסית, חשוב מתמיד. הטכנולוגיה הביאה לשינוי עמוק באופן בו אנו חווים את העולם והשתלבה לחלוטין בחיינו. חדשנות של מוליכים למחצה היא בבירור לב ההתקדמות הטכנולוגית המודרנית המשפיעה על חיינו.

טכנולוגיית היצור ב- 7 ננומטר, שהחלה בייצור המוני בשנת 2018, הייתה קוו פרשת מים בהיסטוריה של מוליכים למחצה. היתה זו הטכנולוגיה המתקדמת הראשונה שהועמדה לרשות כל חברות המוליכים למחצה. קוו פרשת מים זה הוביל למוצרים המשנים את כללי המשחק במגוון רחב של יישומים, כולל ,5G מעבדים מתקדמים , מעבדים לישומים גרפים, טכנולוגיות לתחום הרשת, משחקים ורכב. כיום, טכנולוגיית 7nm של TSMCמאפשרת יצורם של למעלה מ -150 מוצרים בשוק. מגמה זו של דמוקרטיזציה באימוץ הטכנולוגיה תמשיך בהתקדמות מתמדת בקנה מידה ברמת השבב, בשיפור ה- EUV- ובמגוון טכניקות לשיפור מכשירים כגון ערוץ ניידות גבוהה.

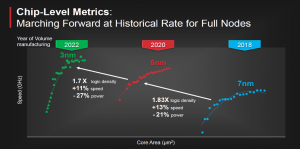

אמנם ההצעות לשיפור טכנולוגיית המכשירים עלולות להאט אך נתוני המוצרים שלנו מראים כי הפחתת הספק באותה מהירות, או עליית מהירות באותו הספק, וצפיפות עדיין ממשיכים את המגמה ההיסטורית בחמש השנים האחרונות עם טכנולוגיות 5 ננומטר ו -3 ננומטר. במבט קדימה, התעשייה והאקדמיה עבדו בשיתוף פעולה הדוק לפיתוח חדשנות במבני טרנזיסטורים חדשים וחומרים חדשים, יחד עם ארכיטקטורת מערכת חדשה ואינטגרציה תלת-ממדית, כדי להמשיך את ההתקדמות הטכנולוגית אף מעבר ל -3 ננומטר.

בואו נסתכל על כמה מאותם חידושים:

לִיתוֹגְרָפִיָה

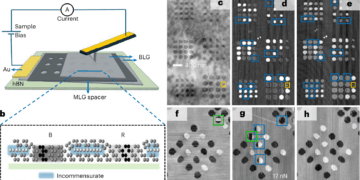

באופן מסורתי הליתוגרפיה הייתה המניע העיקרי להתקדמות בצפיפות היצור. החידוש האחרון של ליתוגרפיה EUV פרץ את צוואר הבקבוק ברזולוציה של ליתוגרפיה טבילה. הוא מספק נאמנות גבוהה יותר לדפוסים, מקצר את זמן המחזור ומפחית את מורכבות התהליכים ושיעורי הפגמים. בנושא תפוקת ה- EUV, אינדיקטור מרכזי הוא כוח המקור. חלה התקדמות מתמדת בכוח המקור של ה– EUV והיא הגיעה כעת ל -350 וואט. זה מאפשר ייצור בנפח גבוה של 5 ננומטר , סולל את הדרך לפיתוח 3 ננומטר ו -2 ננומטר, ומספק דרך להפחתת עלויות ליתוגרפיה לאורך זמן.

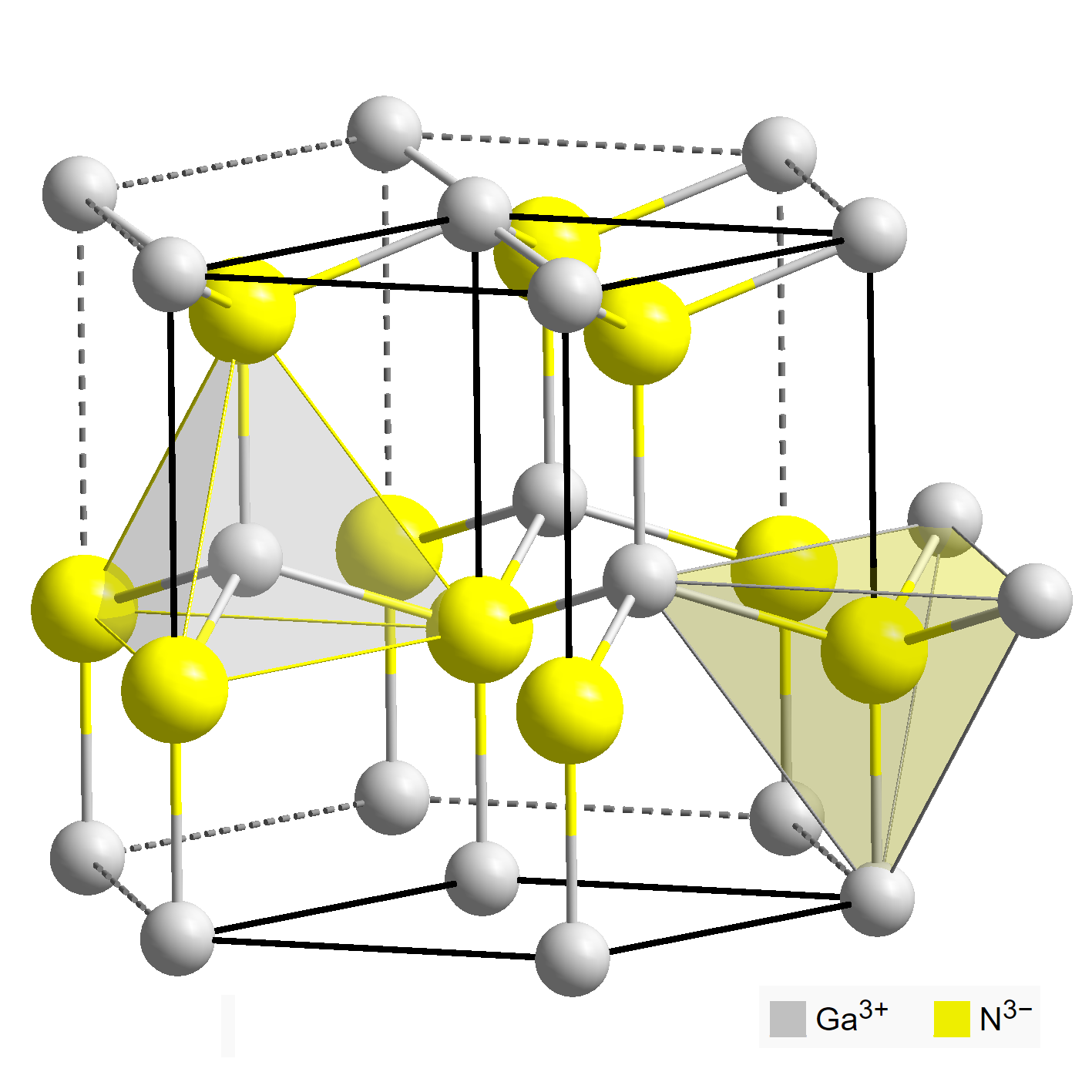

מבנה טרנזיסטור

אנו רואים פריצות דרך משמעותיות במבנה הטרנזיסטור החדש ובחומרים חדשים. בניגוד לדורות קודמים, כאשר קנה המידה של דנארד סיפק את ההנחיה העיקרית לקידום ביצועי המכשירים, הטכנולוגיות הלוגיות משתמשות כיום במגוון חומרים וחידושים במכשירים, המותאמים ביחד עם תכנון מעגלים. בהמשך, מעבר ל FinFET– טרנזיסטור ננו-שכבות עשוי להציע ביצועים נוספים ויעילות הספק. טרנזיסטור ננו-שכבות זה מאפשר הורדת מחסומים (DIBL) והנפת תת סף, כדי להגביר את ביצועי המעגל בהשוואה לדורות הטכנולוגיה הקודמים. שיפורי ביצועי טרנזיסטור מתורגמים ישירות להפעלת VDD נמוכה יותר של .SRAM

אופטימיזציה משותפת של תכנון טכנולוגיה

בכמה דורות הטכנולוגיה האחרונים, אומצה אופטימיזציה משותפת של תכנון שבבים , או DTCO, בשילוב עם קנה מידה פנימי כדי להשיג את צפיפות הלוגיקה הרצויה והפחתת עלויות למינימום. ברצוני לציין שבגלל DTCO מדדי קנה המידה הפנימיים, כגון גובה השער, המגע ומינימום גובה המתכת, אינם משקפים עוד את צפיפות הלוגיקה המעשית של טכנולוגית DTCO והוא מופעל על ידי תכונות טכנולוגיות חדשות של תהליכים כגון אזור מגע-שער פעיל יתר על המידה, הפסקות דיפוזיה בודדות, פינוי אוכלוסיית סנפיר ותכונות שונות בהתאמה עצמית. התוצאה היא גידול של פי 1.8 בצפיפות הלוגיקה, והפחתת משמעותית של גודל שבב ב- 35-40% לאותו תכנון, גם כאשר כלולים האזורים ה"פחות מדרגיים "של השבב, כמו אנלוגי ו I / O- תרומת DTCO צפויה להמשיך ולצמוח בצמתים עתידיים.

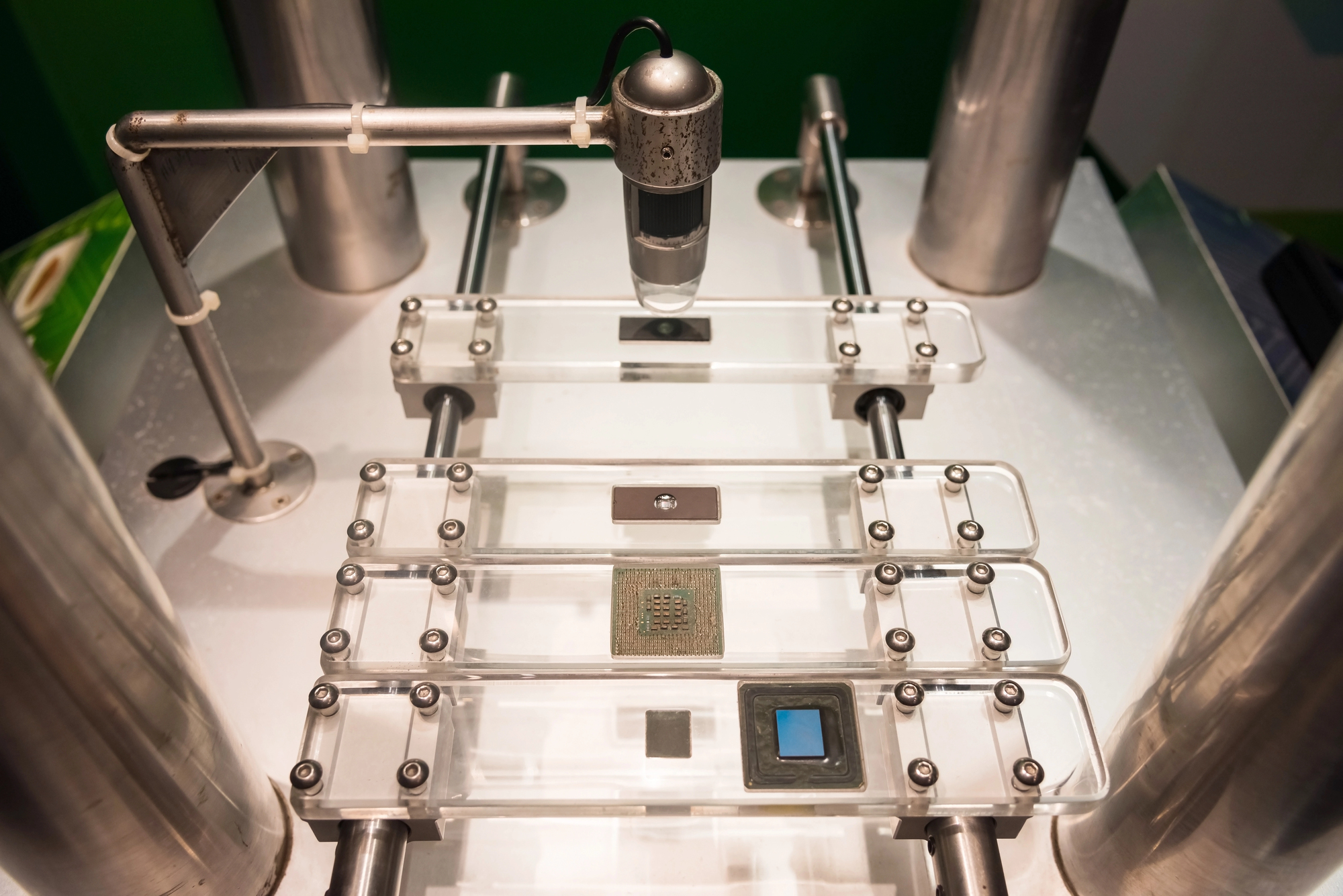

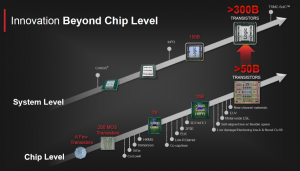

טכנולוגיות שילוב מערכות

ברמת המערכת, פתרונות מרובים, כמו ה- InFO, CoWoS® -ו- TSMC-SoIC ™ של TSMC פתחו דרכים להגדיל את מספר הטרנזיסטורים באריזה אחת ליותר מ -300 מיליארד . התעשייה שלנו כבר החלה להסתכל מעבר להנדסת שבבים בודדים ועברה לשלב כמות שבבים לכלל מערכת.

שבבים אלה, המכונים גם Chiplets הפכו לאחרונה לנושא חם מאוד, אך חלק מהטכנולוגיות החלוציות של שילוב מערכות בתעשייה עשו אינטגרציה של שבבים לפני ש Chiplets הפכו לכאלה פופולארים. לדוגמה, טכנולוגיית CoWoS מיוצרת בהיקפים גדולים מאז 2011, ויצרו יותר מ -90 מוצרים עם תבניות לוגיות המשולבות בתבניות זיכרון, כמו גם תבניות לוגיות המשולבות ביחד עם עוד תבניות לוגיקה, כדי להגביר את הביצועים של המערכת הארוזה.

מערכות עם מספר שבבים ארוזות יחד, ימלאו תפקיד חשוב יותר ויותר. ניתן ליצור התמחיות של שבבים לפונקציות מסוימות ובכך לבצע אופטימיזציה שתביא לשיפור ביצועים, יעילות בצריכת אנרגיה, בצפיפות, בעלות ובפונקציונליות. ההתקדמות האחרונה בטכנולוגיית שילוב מערכות כגוןFabric D3 איפשרה (כלכלית) לחלק מערכת לטכנולוגיות ספציפיות לתחום ולשלב שבבים בצורה הטרוגנית ביחד.

צפיפות החיבור בין שבב לשבב יכולה להשתפר בארבע סדרי גודל נוספים, תוך שימוש ב- SoIC ובתוספות העתידיות שלה, כולל אינטגרציה תלת ממדית מונוליטית. "שילוב מערכת בחבילה" מתגבש כשיטה משלימה להאצת כמות טרנזיסטורים במערכת, לשיפור ביצועים וליעילות אנרגטית.

חסכון באנרגיה

ללא קשר להבדל בגישות טכנולוגיות שונות, דבר אחד נפוץ בכל גישה. יעילות צריכת אנרגיה היא המטרה החשובה ביותר שלנו במחשוב. במהלך 15 השנים האחרונות, התעשייה שלנו סיפקה רמות חדשות של ביצועים, מחשוב יעיל יותר בצריכת אנרגיה, והשיגה קרוב לפי שניים שיפור ביצועים לעומת חסכון באנרגיה בכל שנתיים. מגמה זו כוללת את הטכנולוגיה העדכנית ביותר של 5 ננומטר הנמצאת כעת בייצור המוני. ופיתוח ה- 3 ננומטר של TSMC נמצא בדרך לספק את אותה התקדמות. ביצועי המערכת ויעילות צריכת האנרגיה ימשיכו להתקדם בקצב היסטורי, מונעים על ידי חידושים ממקורות רבים, כולל חומרים, טכנולוגיית מכשירים ואינטגרציה, תכנון מעגלים, תכנון הנדסת מערכת. כאשר הענף שלנו וקהילית המחקר האקדמי ממשיכים לעבוד יחד, אנו נפתח טכנולוגיות שימשיכו מגמה זו גם בעתיד.

שותפות לחדשנות

טכנולוגית יצור חדשה בקצב של אחת לשנתיים תמשיך לספק את הבסיס להשקת מוצרים חדשים. כדי להוציא את הדבר לפועל, נצטרך שותפות של כל השחקנים בכל התעשייה, החל מספקי חומרים וכלי עבודה, ספקי טכנולוגיית מכשירים, מתכנני מעגלים ואדריכלי מערכות וכלה בשותפי המערכת הכלכלית וכן קהילת המחקר האקדמי . חשוב לטפח מערכת כלכלית תכנונית רחבה המורידה את מחסומי הכניסה ומשחררת כמות עצומה של חדשנות בחומרה. באופן אידיאלי, זה צריך להיות קל לשמור על חדשנות בחומרה, כמו לכתוב קודי תוכנה. כשזה יקרה, נוכל לחזות ברנסנס נוסף בתכנון היישומים והמערכות.

לסרטון עם נאומו המלא של ד"ר מארק ליו אותו הציג בכנס ISSCC 2021- בקרו בכתובת: ISSCC2021 – P1 – YouTube