הפלטפורמה מתאימה לשימוש בכל תהליך התכנון של SoCs (מערכות על גבי שבב)

קיידנס דיזיין סיסטמס (Cadence), מפתחת תוכנות לתחום ההתכנון האלקטרוני, הכריזה על Cadence Stratus: פלטפורמת הסינתזה ברמה גבוהה (HLS) הראשונה בתעשייה שמתאימה לשימוש בכל תהליך התכנון של SoCs (מערכות על גבי שבב). דור חדש זה של פלטפורמות משלב אתForte Cynthesizer ומהדר Cadence C-to-Silicon בתוך כלי אחד במטרה לספק שיפור של פי עשרה ביעילות, שיפור של 20% באיכות תוצאות (QoR) של PPA (הספק, ביצועים ושטח), בנוסף לאימות מהיר פי חמישה בהשוואה להליך סיתזת RTL כתובה ידנית.

עד לפלטפורמת ה-Stratus, אף כלי סינתזה ברמה גבוהה לא היה חזק דיו להתאים לשימוש בכל חלקי תכנון ה-SoC, מה שאילץ את המתכננים לבחור את החלקים בתכנון שלהם שבהם יוכלו להשתמש בטכנולוגיה. הודות לשילוב של מערך תכונות מקיף בתוך פלטפורמת ה-Stratus, מבטלת קיידנס את הצורך להתפשר בתכנון.

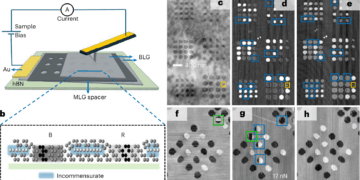

בין התכונות החשובות הללו ניתן לציין את הדור השישי של מנוע מרובה ליבות לסינתזה ברמה גבוהה שמספק יכולת שימוש מצוינת, מדרגיות ואיכות תוצאות בכל מרחב היישום, כולל תכנונים ממוקדי בקרה ותכנונים ממוקדי נתיב, נתונים הכוללים מאות בלוקים. בנוסף, ייהנו המתכננים מאינטגרציה מלאה עם מהדר Cadence Encounter RTL ועם Encounter Conformal ECO Designer, עובדה שתאפשר סינתזה ברמה גבוהה ש"מודעת" הן לנתונים פיסיים ל-ECO (הוראות שינוי הנדסיות) אשר יצמצמו את כמות שינויים Engineering Changes Order. תכונה נוספת היא ספריית IP עשירה של ממשקי I/O וטיפוסי נקודה צפה (customizable floating point), אשר ניתנים להתאמה מיוחדת ויסייעו להגדלת היעילות מכיוון שיעמידו לרשות המתכננים אבני בניין SystemC ממוטבות וניתנות לסינתוז. אוטומציה ו-IDE מלאות של זרימת הכלים ואבלואציה של ריבוי תרחישים יאפשרו חקירה ארכיטקטונית מלאה וישפרו את האימות בזכות סביבה עקבית ממודלים מוקדמים של TLM (מידול

| {loadposition content-related} |