TSMC מאמינה כי ניתן להקטין את צפיפות הטרנזיסטורים עוד יותר. גודפרי צ'נג מסביר כיצד.

עברו כמעט 3 חודשים מאז הצטרפתי ל-TSMC. אחד הנושאים העיקריים בהם התעמקתי מהתחלה היה חוק מור, לפיו – במילים פשוטות – מספר הטרנזיסטורים בהתקן או שבב משולב מכפיל את עצמו מדי שנתיים.

חוק מור למעשה מכונה חוק בשוגג שכן נכון יותר לתאר אותו כקו מנחה לבחינת העבר וחיזוי העתיד ביחס למספר הטרנזיסטורים בהתקן מוליכים למחצה. הבחינות והתחזיות הללו היו במידה רבה נכונות בעשורים האחרונים. עם בואנו לעשור חדש, יש הטוענים שחוק מור מת.

הם מיזגו את חוק מור באופן שבו הביצועים של שבב, בהינתן אותו השטח, מכפילים את עצמם מדי שנתיים. טענה זו הייתה נכונה במשך שנים רבות, ובייחוד בעת פיתוח CPU ו-GPU. החל משנות ה-70' ועד לתחילת שנות ה-2000, חלה עלייה עצומה במהירות שעון הטרנזיסטור, ממגה הרץ יחיד לג'יגה הרץ מרובים. יחד עם זאת, ביצועי המחשוב גדלו מאז שנות ה-2000, לא מתוך שיפור מהירות שעון הטרנזיסטור, אלא באמצעות חדשנות בארכיטקטורת סיליקון והקבלת עומסי מחשוב. חברות נענו להקבלת תוכנה זו בחידושי ארכיטקטורה נוספים ובהוספת ליבות מחשוב נוספות. ככל שקיימות יותר ליבות, כך יכול שבב להתמודד עם יותר מחרוזות מידע ולספק ביצועים משופרים באופן כללי.

מהו המדד לדחיסת יותר טרנזיסטורים לאותו השטח? צפיפות! חוק מור עוסק בצפיפות! צפיפות עוסקת במספר הטרנזיסטורים בשטח דו-מימדי נתון. עלות השבב נגזרת באופן יחסי משטח השבב. המאמר של מור משנת 1965 הבהיר כי קיים קשר בין עלות הייצור לרכיב וסך מספר הטרנזיסטורים שעל שבב.

הבה נבחן כמה מבעיות המחשוב בהן אנו נתקלים היום וכיצד שיפורים בצפיפות ימשיכו לשפר את הביצועים.

ראשית, בואו נתייחס לפיל שבחדר. יש האומרים שחוק מור מת משום שהם אינם מאמינים שאפשר לכווץ את הטרנזיסטור עוד יותר. האתגר הראשי הוא שליטה בחומרים ברמת האטום. כיצד מחברים אטומים נפרדים ליצירת טרנזיסטור? כיצד עושים זאת עבור מיליארדי טרנזיסטורים המצויים על שבב מודרני? כיצד בונים את השבבים הללו, בעלי מיליארדי טרנזיסטורים, באופן משתלם?

כמענה על שאלה זו, TSMC הכריזה לאחרונה על צומת ה-N5P, אשר מגדיל עוד יותר את המובילות שלנו מעבר לצומת N5 אשר יספק את צפיפות הטרנזיסטור הגבוהה ביותר ויציע את הביצועים המהירים ביותר. לאחר שצפיתי במפת הדרכים הטכנולוגית שלנו, אני יכול להצהיר באופן בטוח של-TSMC עוד שנים רבות של חלוציות וחדשנות בהן נמשיך להקטין את הטרנזיסטור היחיד ולשפר את הצפיפות. אתם תשמעו עוד מאיתנו בחודשים ובשנים הקרובות ככל שנתקדם לצמתים חדשים.

במטרה להזין מעבדי בינה מלאכותית ((AI מודרניים ייעודיים, חשוב לספק זיכרון שנמצא קרוב יותר לליבות השואבות את הנתונים לשיפור זמן התגובה ולאספקת רוחב פס גדול יותר של נתונים לעיבוד. זהו היתרון של צפיפות ברמת ההתקן. כאשר הזיכרון קרוב יותר לליבות הלוגיקה, המערכת משיגה זמן תגובה מהיר יותר, צורכת פחות חשמל ומציגה שיפורים בביצועים באופן כללי.

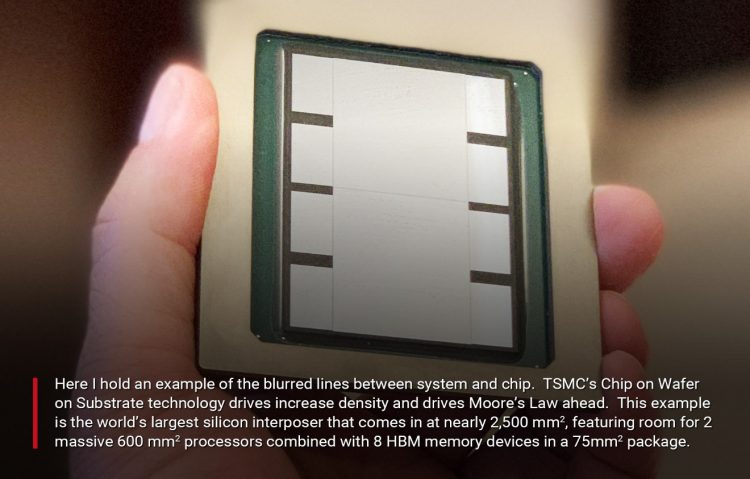

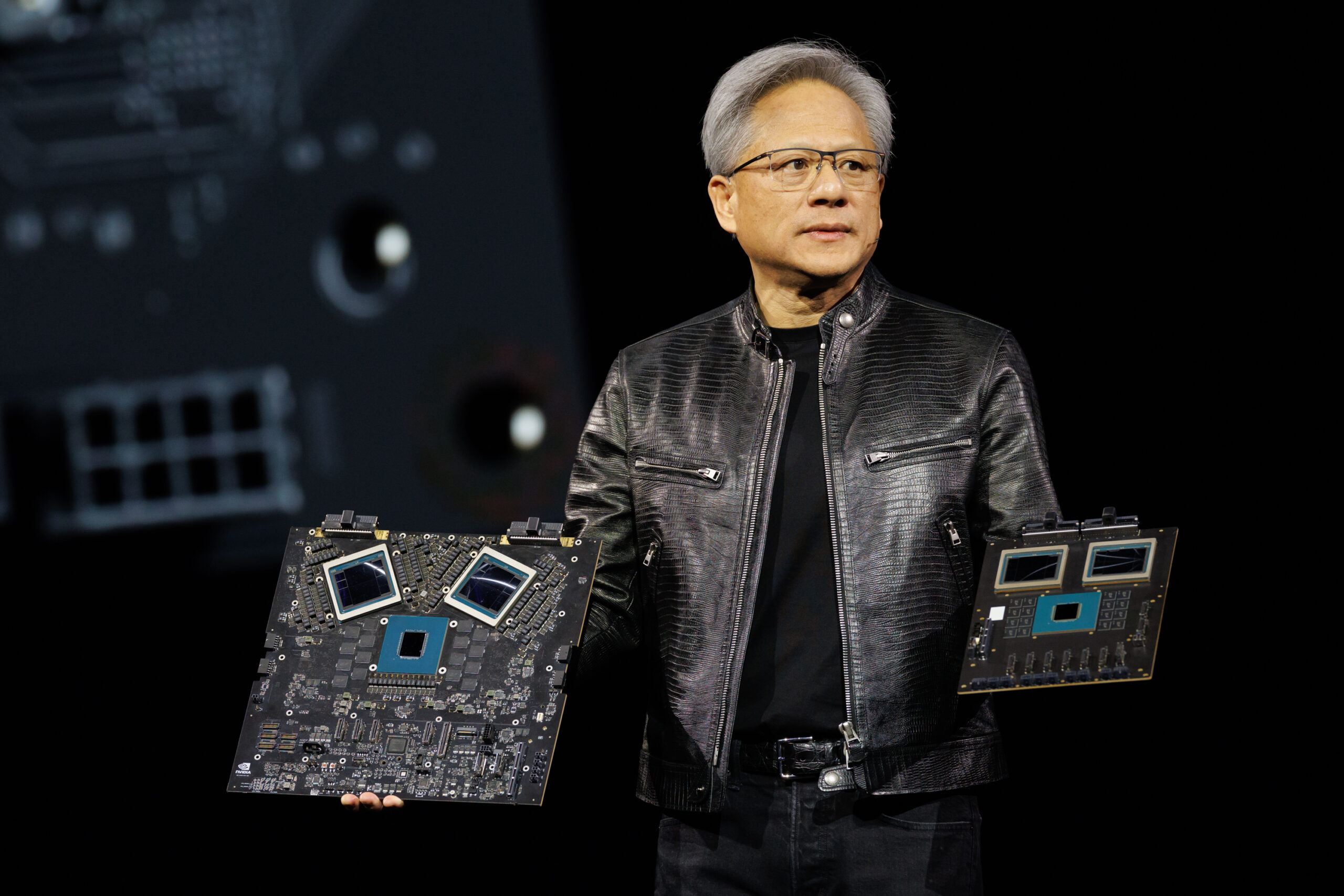

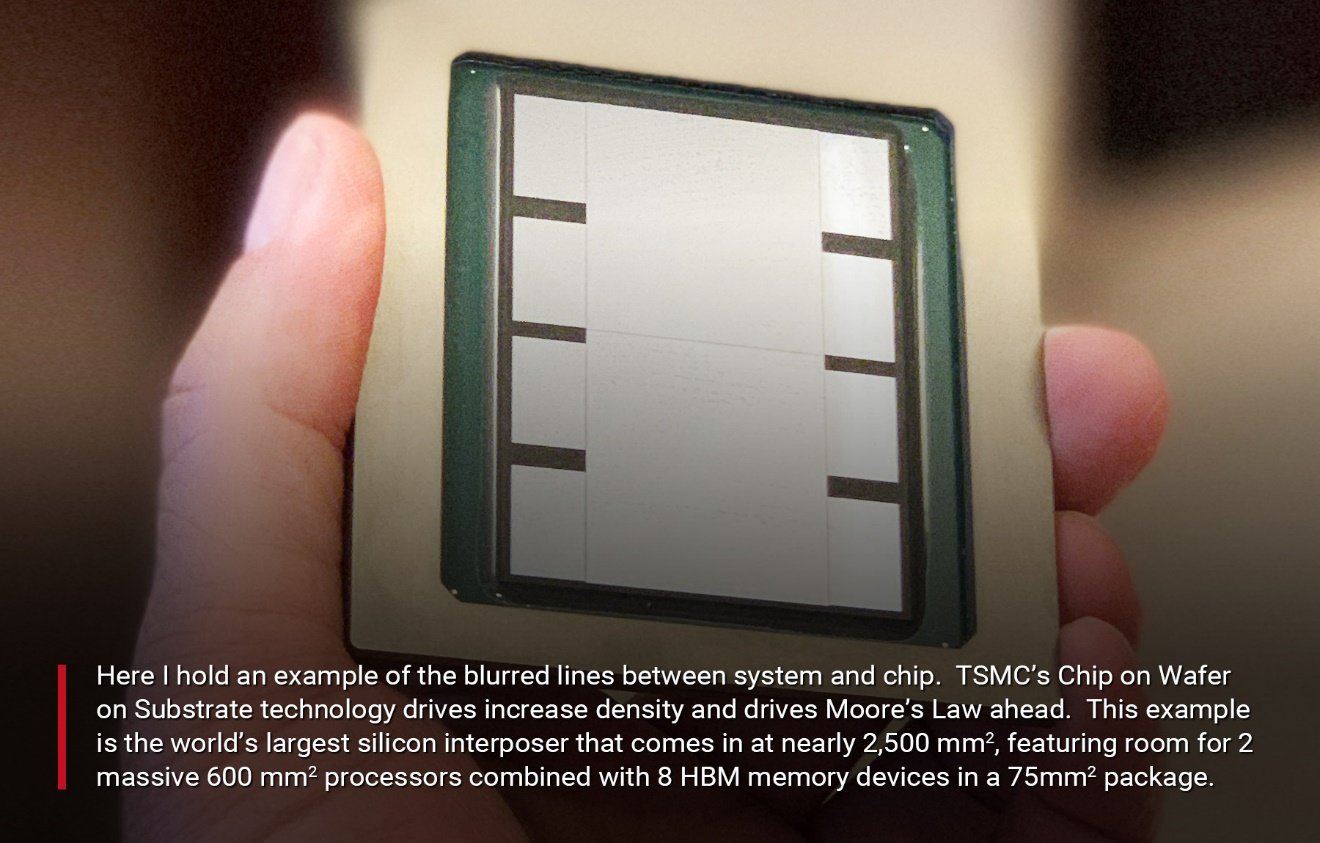

חלקכם ודאי סבורים כי מדובר בעניין ברמת המערכת ולא במאפיין מובנה בטכנולוגיית ההתקן. כבר היום מיטשטש הקו שבין הגדרת שבב להגדרת מערכת. כעת עברנו מעידן של Design-Technology Co-Optimization (DTCO) לעידן של System-Technology Co-Optimization (STCO).

האריזה המתקדמת היום מקרבת את הזיכרון ללוגיקה. בדרך כלל, ליבות לוגיקה מוזנות משבבי זיכרון נפרדות באמצעות ממשקים כגון DDR או GDDR. המרחק הפיזי בין התקן הזיכרון וליבות הלוגיקה מגביל את הביצועים בשל זמן תגובה ארוך יותר. גם רוחב הפס מוגבל בזיכרון דיסקרטי בשל רוחב הממשק המוגבל. בנוסף, צריכת החשמל עבור לוגיקה וזיכרון דיסקרטיים מגדירים את הביצועים הכוללים של ההתקן, שכן היכולת לשחרר את האנרגיה התרמית המוקרנת מהתקנים דיסקרטיים היא מוגבלת.

בינה מלאכותית (AI) נחשבת לעיתים לבעיית מחשוב אחת, אך קיימים שני היבטים ברורים ב-AI: לימוד (למידת מכונה) והסקה. כדי שמערכת AI תוכל לעבוד, יש ללמד רשת עצבית. הלימוד מחייב פעולות מחשוב אינטנסיביות בהם ליבות הלוגיקה מקבלות כמויות עצומות של נתונים. ככל שניתן להזין את ליבות הלוגיקה מהר יותר, כך הלמידה מהירה יותר – כאן רוחב הפס הוא עניין קריטי. באריזת זיכרון עם ליבות לוגיקה, תוכלו לצמצם את צריכת החשמל של למידת AI תוך הגדלה משמעותית של רוחב פס הזיכרון.

הסקת AI היא היישום של הרשת העצבית המלומדת במציאות. מדובר במחשוב ב-Edge. לאחר שלימדתם את הרשת העצבית, התקני Edge צריכים להשתמש בלימוד זה ולבצע את משימותיהם בזמן הקצר ביותר.

TMSC כבר מציעה בשוק אינטגרציה הדוקה של ליבות לוגיקה וזיכרון באמצעות שיטות אריזה מתקדמות. הקו שבין פתרון מוליך למחצה ופתרון מערכתי הולך ומיטשטש ככל ששיטות האריזה המתקדמות מבוססות פרוסות סיליקון. TSMC פיתחה שיטות אריזה מתקדמות המאפשרות ללקוחותינו לספק מערכת שלמה עם חוצץ מבוסס סיליקון או אינטגרציית fan-out based chiplet.

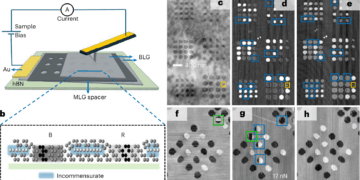

חוק מור עוסק בהגדלת הצפיפות. מעבר לצפיפות המערכתית המושגת באמצעות אריזה מתקדמת, TSMC תמשיך להגדיל את הצפיפות ברמת הטרנזיסטור. בפני TSMC עומדות אפשרויות רבות לשיפור צפיפות טרנזיסטורים בעתיד, לרבות השימוש בטרנזיסטורים המיועדים לחומרים דו מימדיים במקום סיליקון – אנו מתעמקים בטבלה המחזורית. בשימוש בחומרים חדשים אלה, אחד השיפורים האפשריים בצפיפות הוא לערום שכבות טרנזיסטורים מרובות במה שאנו מכנים Monolithic 3D Integrated Circuits. ניתן להוסיף CPU על גבי GPU ועל גבי מנוע AI Edge עם שכבות זיכרון בינהם.

חוק מור לא מת, קיימות עוד דרכים רבות להגדלת הצפיפות!

מאמר זה מפורסם במסגרת מאמרי מגזין TapeOut ובחסות חברת TSMC .

| {loadposition content-related} |