Cadence משיקה IP מתקדם –AI בטכנולוגיית N3P של וחושפת כלי תכנון מבוססי בינה מלאכותית לייצור שבבים מתקדמים

Cadence מודיעה על התקדמות חשובה בתכנון אוטומציית שבבים ורכיבי IP, הודות לשיתוף הפעולה המתמשך שלה עם TSMC לפיתוח תשתיות תכנון מתקדמות והאצת זמן ההגעה לשוק, עבור יישומי לקוח מבוססי בינה מלאכותית (AI) ו-HPC. שיתוף הפעולה הצמוד וארוך השנים בין Cadence ו-TSMC על פני כל הספקטרום, החל ב-EDA (אוטומציית תכנון אלקטרוני) מונע בינה מלאכותית, דרך טכנולוגיות 3D-IC (מספר שבבים באריזה יחידה בשלושה ממדים) וכלה ברכיבי IP ופוטוניקה, הוא שמאפשר ייצור של המוליכים-למחצה המתקדמים ביותר בעולם.

Cadence ו-TSMC עבדו יחד על תשתיות עיצוב עבור טכנולוגיות תהליכים מתקדמות, כולל N2, N3 A16TM ו-A14TM של TSMC, המבוססות על מערכות דוגמת Cadence® Innovus™ Implementation, Quantus™ Extraction Solution ו-Quantus Field Solver, Tempus™ Timing Solution לרבות ECO Option, מערכת Pegasus™ Verification, Liberate™ Characterization Portfolio, Voltus™ IC Power Integrity Solution, Genus™ Synthesis Solution, Virtuoso® Studio ופלטפורמת Spectre® Simulation. תהליכי העבודה משולבי AI של Cadence לתכנון השבבים ועבור 3D-IC זמינות כעת עבור טכנולוגיות N2, N3 ו- A16TMשל TSMC, כמו גם עבור תכונות חדשות בייצור אריזות מתקדמות 3DFabric. כמו כן, Cadence משתפת פעולה עם TSMC בפיתוח EDA עבור תהליך A14 של TSMC, כשה-PDK (חבילת קבצי התכנון) הראשון שלה צפוי לצאת לשוק בהמשך השנה. בנוסף, כמה רכיבי IP של Cadence כבר מוכנים לשימוש מסחרי (Silicon Proven) וזמינים עבור תהליכי ייצור בטכנולוגיית N3P של TSMC.

צ'ין-צ'י טנג, סמנכ"ל בכיר ומנכ"ל קבוצת Digital and Signoff ב- :Cadence"Cadence ו-TSMC ממשיכות להיות מחויבות להאצת ושיפור תהליכי התכנון של שבבי סיליקון מתקדמים עבור לקוחותינו. אנו מסייעים למתכננים לפתח את הדור-הבא בבינה מלאכותית ו-HPC באמצעות תמיכה בטכנולוגיות המובילות של TSMC על ידי תכונות בינה מלאכותית, רכיבי IP ואף מעבר לכך".

אביק סארקאר, מנהל אגף ניהול אקוסיסטם ושותפויות ב-TSMC: " TSMCיחד עם שותפינו בתחום ה- Open Innovation Platform)– OIP) כדוגמת Cadence, מתמודדת עם כמה מהאתגרים המורכבים ביותר בפיתוח שבבים, במטרה להביא לביצועים ויעילות אנרגטית גבוהים יותר במערכות מבוססות בינה מלאכותית. השותפות ארוכת-השנים בינינו ממשיכה ומאפשרת ללקוחותינו המשותפים להאיץ את הדרך לסיליקון במקביל לכך שהיא מביאה להתרחבות מהירה של טכנולוגיות בינה מלאכותית".

פתרונות תכנון מבוססי-AI של צ'יפים לטכנולוגיות תהליכים מתקדמות של TSMC

Cadence ו-TSMC חברו יחד לפיתוח פתרונות תכנון מבוססי AI עבור לקוחותיהם, המאפשרים פיתוח שבבים עם אופטימיזציית הספק, ביצועים ושטח (PPA) מיטבית, בטכנולוגיית N2 של TSMC. במסגרת תהליך התכנון הדיגיטלי המלא של Cadence, הפעילה TSMC את Cadence JedAI Solution, את טכנולוגיית היישומים מבוססת הבינה המלאכותית של Cadence – Cerebrus® Intelligent Chip Explorer, לרבות תכונות לשיפור התפוקה המונעות על ידי עוזר הבינה המלאכותית Innovus+. כמו כן, ביצעה ולידציה של תכונות מבוססות-AI נוספות, כגון סיוע אוטומטי בתיקון הפרות של כללי התכנון (DRC), מה שמאפשר השלמה מהירה יותר ויעילות גבוהה יותר בפיתוח שבבי AI באמצעות טכנולוגיית N2 של TSMC.

הגברת התפוקה של תכנון מבוסס טכנולוגיית 3D-IC

פתרונות 3D-IC של Cadence מספקים תמיכה מקיפה לפתרונות האריזה המתקדמים ולתצורת שבבים במערום (die stacking) במסגרת טכנולוגיית 3DFabric של TSMC. החידושים האחרונים כוללים יכולות אוטומציה עבור חיבורי bump, יישומים וניתוח פיזיים של מספר צ'יפלטים במקביל והוספה חכמה של סמני יישור. יישום ה-AI של Cadence, Clarity™ 3D Solver ופלטפורמת Sigrity™ X בשילוב עם Optimality™ Intelligent System Explorer מאפשר ביצוע אוטומציה לניתוח ואופטימיזציה של SI/IP ברמת המערכת, המבוסס על 3Dblox. לקוחות המשתמשים בזרימת ייחוס בעל אורכי-גל מרובים של המנוע האוניברסלי הפוטוני והקומפקטי מבית TSMC (TSMC-COUPE™) יכולים להפעיל את Virtuoso Studio עם Celsius™ Thermal Solver, לרבות משפר התפוקה שפיתחו TSMC ו-Cadence, הכולל טכניקות מתקדמות של סימולציה תרמית, המפחיתות את הסיכון לירידה בביצועים החשמליים והפוטוניים.

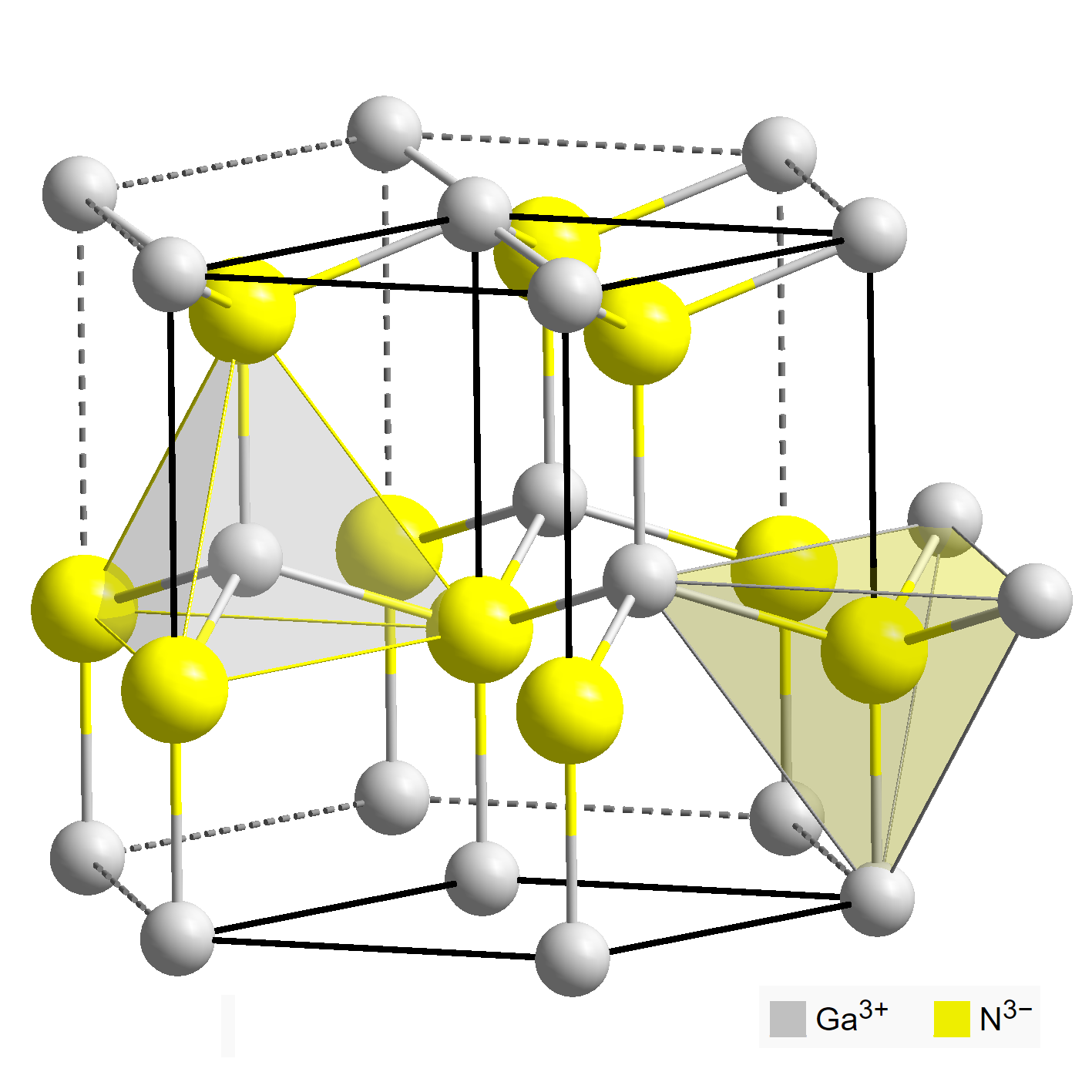

רכיבי IP פורצי-דרך עם טכנולוגיית N3P של TSMC

Cadence ממשיכה להוביל חדשנות בתחום ה-AI וה-HPC באמצעות מתן פתרונות IP מתקדמים מוכנים לשימוש מסחרי (Silicon-Proven) בטכנולוגיות התהליכים המתקדמות של TSMC, כולל טכנולוגיית N3P ותומכת בלקוחות בבניית מערכות מהירות, יעילות וסקלביליות יותר. רכיבי ה-IP של Cadence מאפשרים תשתית מבוססת-AI על ידי מתן מענה לצורכי רוחב-פס וזיכרון של מודלים מהדור-הבא בתחום ה-AI LLM, Agentic AI ועומסים חישוביים כבדים נוספים. ה-IP החדש של Cadence בטכנולוגיית N3P כולל את ה-HBM4 הראשון ב-N3P, ממשקי זיכרון מהירים כמו LPDDR6/5X במהירות 14.4G, ו-DDR5 MRDIMM Gen2 IP במהירות 12.8G, המספקים ללקוחות מגוון רחב של אפשרויות להתמודדות עם בעיית "קיר הזיכרון" המגבילה מערכות חישוב מבוססות-AI. בנוסף, Cadence מובילה גם בתחום הקישוריות עם IP של PCI Express® (PCIe®) 7.0 המגיעה למהירות של 128GT/s ול-224G SerDes עבור תשתיות AI, וכן ה-eUSB2V2 הראשון וה-IP של Universal Chiplet Interconnect™ (UCIe™) במהירות 32G, התומכים באקוסיסטמים המתפתחים של AI PC ושל צ'יפלטים, ומדגימים את מחויבותה של Cadence לקידום פתרונות חסכוניים באנרגיה וסקלביליים עבור עומסי העבודה של העתיד.יחד, Cadence, TSMC והאקוסיסטם של OIP מאפשרים את הנעת מחזור העל של הבינה המלאכותית קדימה דרך ייעול מסע הלקוח משלב התכנון ועד הסיליקון, מה שמביא את לקוחותיהם להגברת תפוקת התכנון והייעול האנרגטי.