DAC 47th digest: what you missed even if you were there

Dr. Olivier Coudert

No doubt that for the next two weeks you will find many DAC reports in blogs and corporate marketing websites. So I tried not to write yet another DAC report, with a long list of companies and products.

” .

DAC 47th digest: what you missed even if you were there

Dr. Olivier Coudert

![]()

DAC 47th digest: what you missed (even if you were there)

Dr. Olivier Coudert

![]()

was held June 13-18 at the Anaheim Convention Center in California. The preliminary attendance numbers are reported as follow:

Instead, I have chosen to share my absolutely non-exhaustive, completely biased view of DAC. I will then publish a couple of posts focused on specific themes in the next few days.

Attendance

The 47th DAC was held June 13-18 at the

• Total full conference: 1554

• Total exhibit attendees: 3444 (24% international)

• Exhibitors, visitors, and guests: 2557

• Total attendees: 6001

The final attendance numbers are usually a few percent higher.

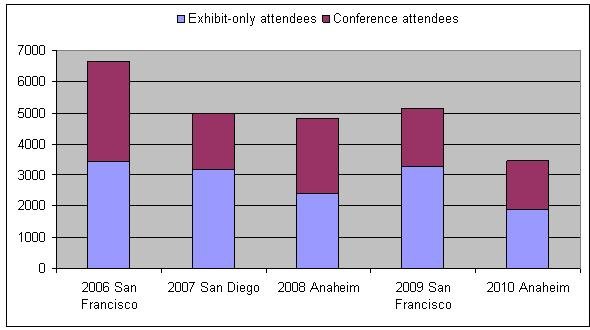

For a fair comparison, I pulled out the preliminary attendance numbers of the past conferences. I was first fooled by the way the numbers were labeled this year –see the comments below, and a big thanks to Sean to bring me the correct interpretation. The table below shows the correct data, excluding booth staff. It shows a sharp decline (33%) of the total attendance compared to last year in San Francisco. Not having DAC in San Francisco means higher cost for most of the attendees –many of them are from the Silicon Valley–, which is clearly reflected in the attendance numbers. But if we compare this year’s numbers with the 2008 DAC venue held at the same location, we see the same sharp decline (28%). Note the drop in exhibits-only attendees (-41% w.r.t. 2009, -21% w.r.t. 2008), not a good sign as this number captures most of the customer audience.

DAC preliminary attendance numbers (not including booth staff)

This year’s DAC comes after one of the worst recession, but looking forward to a very strong semiconductor growth in 2010 and 2011, which should eventually translate into a mildly better business for EDA. The exhibition was well attended on Monday, with a sharp decline on Wednesday –lots of people left by that time.

The buzz

With Cadence’s EDA360 campaign in the background, and the fresh acquisitions of Denali by Cadence and Virage Logic by Synopsys, it felt that IP was the buzzword of the day. IP design here, IP verification there, verification IP everywhere, the overall SoC design looked like an IP integration problem that EDA was gearing up to take on. Embedded software and ESL were also showcased by Cadence and Mentor Graphics as part of their SoC focus.

Verification

There was a booth dedicated to UVM/OVM (Universal Verification Methodology/Open Verification Methodology). These methodologies offer open and interoperable verification solutions. They both support multiple languages and simulators, and enable verification IP, so critical to SoC design. The message was well received and had a strong attendance.

Still on the verification side, new products and startups are trying to repeat the success Certess (acquired by SpringSoft last year Advanced formal verification tools (e.g., property checkers) are slow to find acceptance by the design community. Instead these new products and startups leverage the existing test bench and simulation methodology in place to produce better coverage or faster simulation. Notably missing in this space was NuSym, a no-show at this year’s DAC, confirming the rumors that the startup that demonstrated “intelligent” simulation two years ago is actively looking for a buyer.

The whole simulation and emulation space was strong. Mentor’s Veloce is showing impressive numbers, and is ready to take on Cadence’s Palladium. Eve will likely take notice, and this may bring it closer to Synopsys.

Magma’s Tekton offers sign-off quality multi-mode/multi-corner static timing analysis for multi-million gate circuits. The tool has been designed from the ground up, and tailored for multi-threading and distributed systems. It is a clear competitor to Synopsys’ PrimeTime, even though running PrimeTime *is* the signoff for most customers.

Design and implementation

On the P&R and backend side, nothing really stood out. Synopsys clearly gained in QoR, Mentor’s momentum with Sierra’s Olympus is still strong, and Magma keeps lagging behind, especially in runtime. Atoptech and Azuro, although showing pretty good numbers (verified at customers’), are still considered more like add-ons that comprehensive solutions. This segment looks more and more commoditized, and only the high-end (20nm and below) and 3D seem to offer new growth opportunities in that space.

Oasys, the darling of last year’s DAC, did not make as much as a splash this time, despite its recent announcement with Juniper Networks and Xilinx. Nobody question the speed and capacity of their tool, as well as the clock cycle it can achieve. But some raised concerns regarding the area of their netlists for ASIC.]

On the fringe

This is the “stuff I liked that may be too small to be noticed”, even more so since two of these three companies didn’t have a booth at DAC…

Low power is still under-represented, even though power gets worse with smaller geometries, and power management remains mostly a very manual process. In that space I liked Docea Power, which can simulate system-level models to analyze power consumptions and thermal behaviors. System-level analysis can bring the biggest power savings. It also has a significant impact on the packaging, which is still a domain where conservative approaches are preferred to more cost-efficient, but riskier, choices.

A comprehensive system-level design framework is really an IDE (Integrated Development Environment) for SoC, where hardware and software can be designed together, written and simulated together, and where the HW/SW tradeoffs can easily be explored. IDEs have been used in software for a long time, but are a novelty to hardware designers. Sigasi proposes an IDE for VHDL –what Microsoft’s Visual Studio is to C++. Although this is still light-years away from a SoC IDE, this is a hint into the future of writing RTL.

We heard several claims that cloud computing is coming to EDA (or the converse?). Xuropa best illustrates that (slow) move. They provide turn-key online community solutions for the electronic design industry. Their main customers, Cadence and Synopsys, are using the services for CRM and virtual demo only. But Xuropa could become a platform that enables collaborative design in the cloud, providing secured access to a multi-vendor flows. More on this in a future post.

Last words

Dr. Olivier Coudert has 20 years experience in software architecture and EDA product development, including 10 years in research. He received his PhD in Computer Sciences from Ecole nationale supérieure des Télécommunications, Paris , France , in 1991. He has published 50+ papers and book chapters, and he holds several patents on combinatorial optimization and physical synthesis. He is a recognized expert in the fields of formal verification, logic synthesis, low power, and physical synthesis. He led the development of several EDA products, including 3 from scratch in a startup environment. You can follow Olivier on Twitter, meet him on LinkedIn, or read his blog.

| {loadposition content-related} |